Additionen und Subtraktionen sind grundlegende Operationen in einem digitalen System. Kontrollsystem & digitale Signalverarbeitung . Diese Systeme werden von den Addierern und Subtrahierern beeinflusst, indem sie genaue und schnelle Operationen liefern. Addierer und Subtrahierer spielen in digitalen Systemen eine wesentliche Rolle, da sie in anderen digitalen Operationen wie Multiplikation, Subtraktion und Division weit verbreitet sind. Daher verbessert die Verbesserung der Leistung dieser die Ausführung von Binäroperationen innerhalb einer Schaltung. Die Leistung der digitalen Schaltung kann geschätzt werden, indem die Betriebsgeschwindigkeit, der Layoutbereich und die Verlustleistung bewertet werden. Dieser Artikel beschreibt eine Übersicht über den parallelen Addierer und den parallelen Subtrahierer.

Was sind Paralleladdierer und Parallelsubtrahierer?

Die Parallele Addierer und paralleler Subtrahierer diskutieren hauptsächlich seine Definitionen, Arbeitsweise, Vor- und Nachteile.

Was ist ein Paralleladdierer?

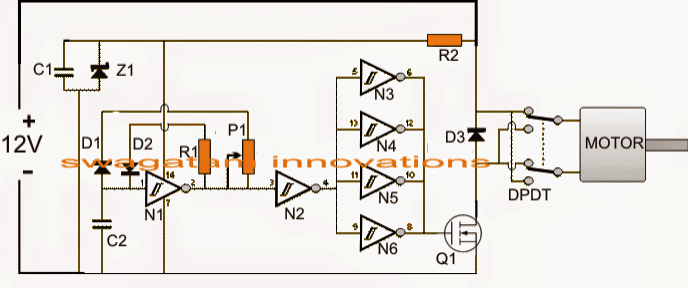

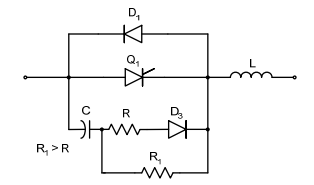

Eine digitale Schaltung, die zum Addieren von zwei Binärzahlen und einem I / P-Übertrag verwendet wird, wobei die Länge eines Bits größer als ein anderes Bit ist und parallel zu äquivalenten Bitpaaren arbeitet. Die Anordnung der parallelen Addierer kann durch Anordnen der Volladdierer (FAs) in einem Kettenmodell erfolgen, in dem der Übertrag o / p von jedem ist Volladdierer (FA1) kann mit dem Übertrags-I / P des nächsten Volladdierers (FA2) innerhalb der Kette verknüpft werden. Das Diagramm des Paralleladdierers ist unten gezeigt.

Paralleladdierer

Die Operation eines n-Bit-Paralleladdierers kann unter Verwendung von n-Volladdierern erfolgen. In ähnlicher Weise sind für den 2-Bit-Paralleladdierer zwei Addierer erforderlich. Im Allgemeinen enthalten diese Addierer die Logik von tragen Sie vorausschauen um sicherzustellen, dass die Ausbreitung des Tragens zwischen der Zugabe der nächsten Stufe die Geschwindigkeit der Zugabe nicht einschränkt.

Arbeiten von Parallel Adder

Das Paralleladdierer-Diagramm ist oben gezeigt. Bei dem ersten Volladdierer wie FA1 kann die Summe wie 'S1' durch Addition von A1 & B1 mit dem Übertrag 'C1' erzeugt werden. Der Übertrag 'C2' ist mit dem zweiten Addierer in der Kette verbunden.

Danach verwendet der zweite Volladdierer wie FA2 das Übertragsbit 'C2', um die Eingangsbits A2 und B2 einzufügen, um die Summe der Übertragungen S2 und C3 zu erzeugen. In ähnlicher Weise wird dieser Prozess für die verbleibenden Volladdierer fortgesetzt, bis der n-te Volladdierer das Cn-Übertragsbit verwendet, um seine Eingaben wie An & Bn einzufügen, um das letzte Bit des O / P mit Cout (letztes Übertragsbit) zu erzeugen.

Was ist ein paralleler Subtrahierer?

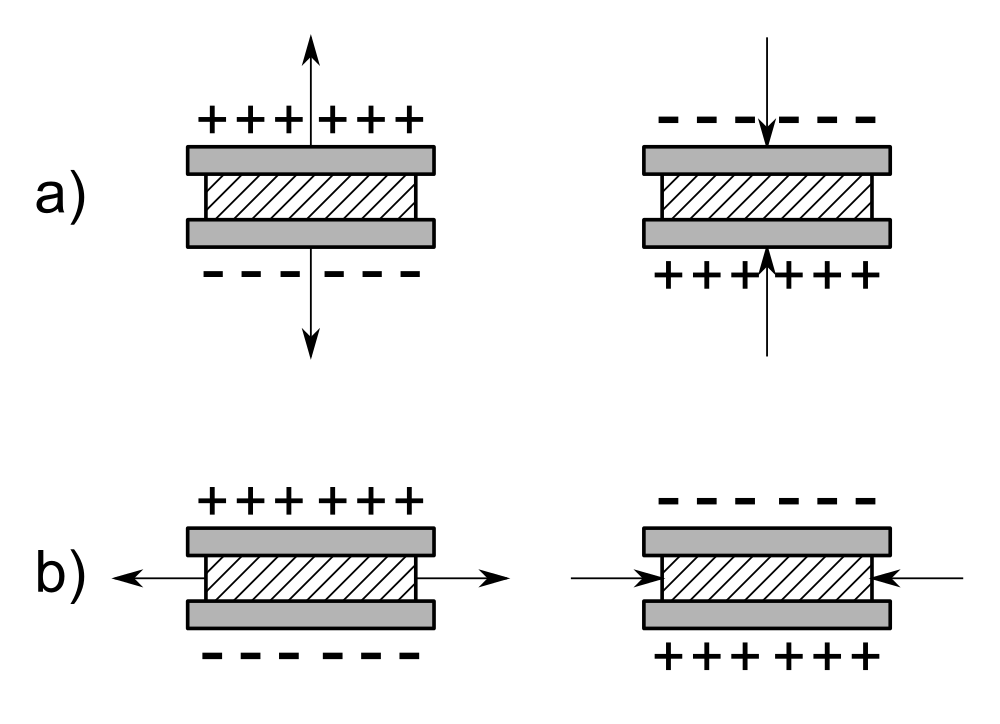

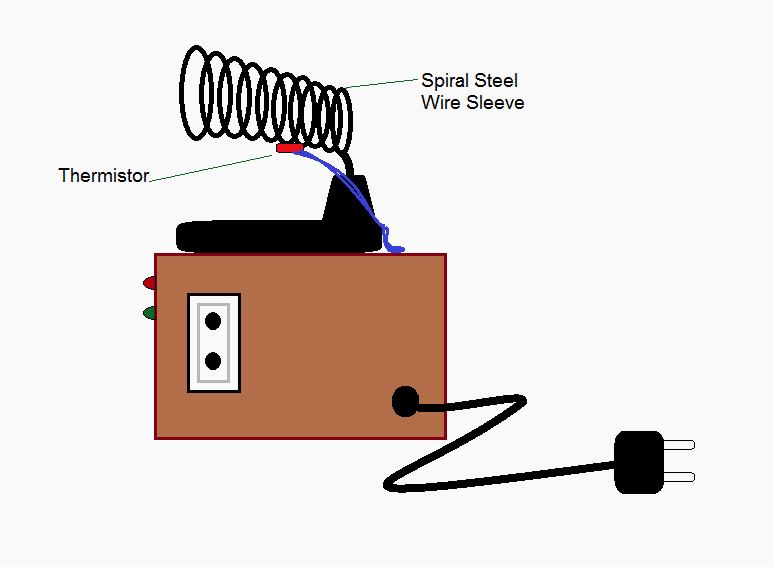

Eine digitale Schaltung, die zur Berechnung der arithmetischen Differenz zwischen zwei binären Bitpaaren verwendet wird, ist als paralleler Subtrahierer bekannt. Hier in Binärbits ist die Länge eines Bits höher als bei anderen Bits. Das Entwerfen dieses Subtrahierers kann auf verschiedene Arten erfolgen, beispielsweise durch eine Kombination aller vollständigen Subtrahierer oder halben und vollständigen Subtrahierer oder aller FAs mit dem i / p des Subtrahend-Komplements. Das Diagramm des parallelen Subtrahierers ist unten gezeigt.

Parallel-Subtrahierer

In dem parallelen n-Bit-Subtrahierer kann das gewünschte o / p durch Kaskadieren der n vollständigen Subtrahierer erreicht werden. Die Verbindung ist ähnlich wie beim 4-Bit-Paralleladdierer. Die Subtraktion davon kann von jedem Bit zu seinem parallelen Bit erfolgen. Wenn ein Kredit generiert wird, breitet er sich während der Kaskade von aus voller Subtrahierer .

Arbeiten des parallelen Subtrahierers

Wie im obigen parallelen Subtrahierdiagramm gezeigt, kann der Subtrahierer mit einer Kombination aller FAs mit dem Subtrahend-Komplement i / p angeordnet werden.

Das Subtraktionsverfahren kann durchgeführt werden, indem die Addition von Minuend mit dem 2er-Komplement von Subtrahend berücksichtigt wird. Damit kann eine parallele Subtraktion durchgeführt werden.

Das Zweierkomplement einer Zahl kann durch Umwandeln der Binärzahl in das 1er-Komplement erfolgen. Hier besteht das Komplement von 1 darin, die Binärzahl zu negieren. Hier kann durch Hinzufügen von 1 zum LSB-Bit des 1-Komplements das 2-Komplement erreicht werden.

Durch die Nutzung Logikgatter kann das 1-Komplement von 'B' durch das NICHT-Logikgatter erreicht werden und '1' wird während des Übertrags hinzugefügt, um das 2-Komplement von 'B' zu erhalten. Außerdem wird dies zu 'A' hinzugefügt, um die arithmetische Subtraktion durchzuführen.

Diese Prozedur wird bis zum endgültigen Volladdierer wie 'FAn' fortgesetzt und verwendet das Übertragsbit 'Cn', um es mit seinem i / p 'An' aufzunehmen, sowie das 2er-Komplement von 'Bn', um das endgültige o / p-Bit mit zu erzeugen letztes Übertragsbit 'Cout'.

Vorteile

Das Vorteile eines Paralleladdierers und Subtrahierers das Folgende einschließen.

- Die Operation dieses Addierers oder Subtrahierers ist im Gegensatz zum seriellen Addierer oder Subtrahierer schneller.

- Die erforderliche Zeit für das Hinzufügen hängt nicht von der Ziffer der Bits ab.

- Alle Bits in diesem werden gleichzeitig addiert oder subtrahiert, so dass das O / P in paralleler Form vorliegt.

- Es ist nicht teuer.

- Diese sind schneller als serielle Gegenstücke.

Nachteile von Parallel Adder / Parallel Subtractor

Das Nachteile eines Paralleladdierers und Subtrahierers das Folgende einschließen.

- In einem Kettenprozess muss jeder Volladdierer auf den Übertrag des vorherigen Addierers warten.

- Jeder Addierer / Subtrahierer im Kettenprozess erhält sofort Eingaben in seine Ports. Die Ports wie Carry oder Borrow erhalten ihre I / Ps jedoch erst, wenn der vorherige Addierer / Subtrahierer ihren Vorgang abgeschlossen hat.

- Es ist also eine Verzögerung aufgetreten, die sich summiert, sobald die Nr. der FAs oder vollen Subtrahierer steigt.

- Frühere Übertragungen sind im Additionsprozess nicht enthalten.

- Daher ist es nicht für die Kaskadierung geeignet, die bei der Multi-Bit-Addition verwendet wird.

- Sobald FAs innerhalb einer Kettenanordnung verwendet werden, kann die Fähigkeit des Ausgangsantriebs verringert werden.

FAQs

1). Was ist der Addierer?

Eine digitale Schaltung, die zum Hinzufügen von Zahlen verwendet wird

2). Was ist Subtrahierer?

Eine elektronische Logikschaltung zur Berechnung der Unähnlichkeit zwischen zwei Binärzahlen.

3). Was sind die verschiedenen Arten von Addierern?

Sie sind Halbaddierer, Volladdierer und Mehrbitaddierer.

4). Was sind Multi-Bit-Addierer?

Sie sind serielle Addierer und parallele Addierer.

Hier geht es also um einen Überblick über die Parallele Addierer und Subtrahierer und ihre Vor- und Nachteile. Addierer sowie Subtrahierer werden häufig in der arithmetischen Logikeinheit eines Computers zur Berechnung der Addition und in CPU und GPU für Grafikanwendungen verwendet, um die Komplexität der Schaltung zu verringern. Hier ist eine Frage für Sie, was ist der Unterschied zwischen Addierer und Subtrahierer?