Im Allgemeinen ist der vollständige Subtrahierer einer der am häufigsten verwendeten und wesentliche kombinatorische Logikschaltungen . Es ist ein grundlegendes elektronisches Gerät, mit dem zwei Binärzahlen subtrahiert werden. In dem früheren Artikel haben wir bereits die grundlegende Theorie von gegeben Halbaddierer & Volladdierer welches die Binärziffern für die Berechnung verwendet. Ebenso verwendet der Vollsubtrahierer Binärziffern wie 0,1 für die Subtraktion. Die Schaltung davon kann mit Logikgattern wie ODER-, Ex-ODER-, NAND-Gatter aufgebaut sein. Die Eingänge dieses Subtrahierers sind A, B, Bin und die Ausgänge sind D, Bout.

Dieser Artikel enthält eine Idee zur Theorie des vollständigen Subtrahierers, die die Prämissen wie Subtrahierer, Design mit Logikgattern, Wahrheitstabelle usw. umfasst. Dieser Artikel ist nützlich für Ingenieurstudenten, die diese Themen im HDL-Praktikum durchgehen können.

Was ist ein Subtrahierer?

Die Subtraktion der Binärziffern kann mit Hilfe der Subtrahiererschaltung erfolgen. Dies ist eine Art von kombinatorischer Logikschaltung, die verwendet wird, um die Subtraktion von zwei Binärziffern wie 0s und 1s durchzuführen. Die Subtraktion von Binärziffern von 0 bis 0 oder 0 bis 1 ändert das Ergebnis nicht. Die Subtraktion von 1 bis 1 ergibt 0, aber die Subtraktion von 1 bis 0 muss ausgeliehen werden.

Zum Beispiel enthält die Zwei-Bit-Subtrahiererschaltung zwei Eingänge wie A & B, während die Ausgänge Differenz und Ausleihe sind. Diese Schaltung kann mit Addierern zusammen mit Wechselrichtern aufgebaut werden, die sich zwischen jedem Dateneingang sowie einem Ausleiheingang (Bin) der früheren Phase von FA befinden.

Subtrahierer werden in zwei Typen eingeteilt, wie Halb-Subtrahierer und Voll-Subtrahierer. Hier diskutieren wir den vollständigen Subtrahierer.

Was ist ein vollständiger Subtrahierer?

Es ist ein elektronisches Gerät oder Logikschaltung Dies führt eine Subtraktion von zwei Binärziffern durch. Es ist eine kombinatorische Logikschaltung, die in der digitalen Elektronik verwendet wird. Viele kombinatorische Schaltungen sind in verfügbar Technologie für integrierte Schaltkreise nämlich Addierer, Codierer, Decodierer und Multiplexer. In diesem Artikel werden wir seine Konstruktion unter Verwendung eines halben Subtrahierers und auch der Begriffe wie Wahrheitstabelle diskutieren.

Voller Subtrahierer

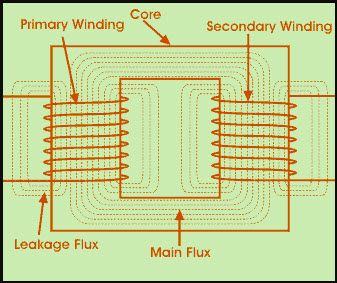

Das Entwerfen hierfür kann durch zwei Halb-Subtrahierer erfolgen, die drei Eingaben wie Minuend, Subtrahend und Ausleihen umfassen. Das Ausleihbit unter den Eingaben wird aus der Subtraktion von zwei Binärziffern erhalten und vom nächsthöheren Paar von subtrahiert Bits, Ausgänge als Differenz und Ausleihen.

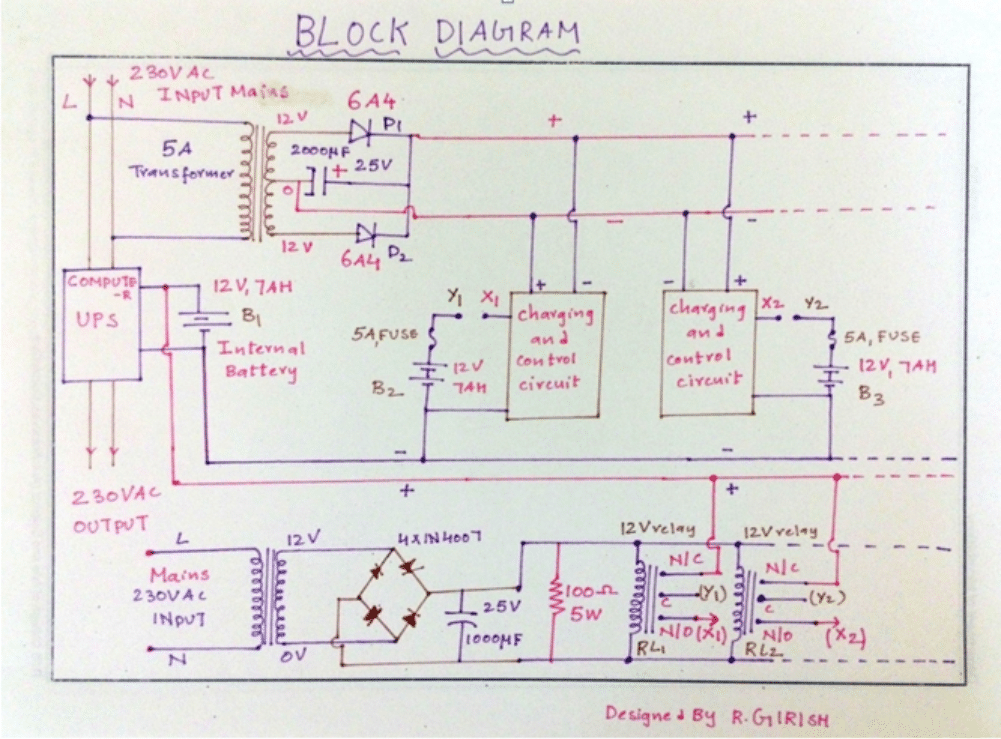

Das vollständiges Subtrahierer-Blockdiagramm wird unten gezeigt. Der größte Nachteil des halben Subtrahierers ist, dass wir in diesem Subtrahierer kein Borrow-Bit erstellen können. Während wir in seinem Design tatsächlich ein Borrow-Bit in der Schaltung erstellen und mit den verbleibenden zwei i / ps subtrahieren können. Hier ist A minuend, B ist subtrahend und Bin ist ausgeliehen. Die Ausgänge sind Difference (Diff) & Bout (Borrow out). Die vollständige Subtrahiererschaltung kann erhalten werden, indem zwei halbe Subtrahierer mit einem zusätzlichen ODER-Gatter verwendet werden.

Vollständiger Subtrahierer-Schaltplan mit Logikgattern

Das Schaltplan des Vollsubtrahierers mit Basisgatter s ist im folgenden Blockdiagramm dargestellt. Diese Schaltung kann mit zwei Halb-Subtrahierer-Schaltungen durchgeführt werden.

In der anfänglichen Halb-Subtrahierer-Schaltung sind die Binäreingänge A und B. Wie wir im vorherigen Halb-Subtrahierer-Artikel besprochen haben, werden zwei Ausgänge erzeugt, nämlich Differenz (Diff) und Ausleihen.

Voller Subtrahierer mit Logic Gates

Die Differenz o / p des linken Subtrahierers wird der linken Halb-Subtrahierer-Schaltung gegeben. Der Diff-Ausgang wird ferner an den Eingang der Subtrahiererschaltung der rechten Hälfte geliefert. Wir haben die Ausleihe in Bit über die anderen I / P des nächsten angeboten halbe Subtrahiererschaltung . Noch einmal wird es Diff geben sowie das Bit ausleihen. Die endgültige Ausgabe dieses Subtrahierers ist die Diff-Ausgabe.

Andererseits ist das Ausleihen aus beiden halben Subtrahiererschaltungen mit dem ODER-Logikgatter verbunden. Später als die ODER-Logik für zwei Ausgangsbits des Subtrahierers auszugeben, erhalten wir die endgültige Ausleihe aus dem Subtrahierer. Das letzte Ausleihen, um das MSB zu kennzeichnen (ein höchst wichtiges Bit).

Wenn wir den internen Schaltkreis beobachten, sehen wir zwei Halb-Subtrahierer mit NAND-Gatter und XOR-Gatter mit einem zusätzlichen ODER-Gatter.

Vollständige Subtraktor-Wahrheitstabelle

Dies Subtrahiererschaltung führt eine Subtraktion zwischen zwei Bits aus, die 3 Eingänge (A, B und Bin) und zwei Ausgänge (D und Bout) haben. Hier geben die Eingaben Minuend, Subtrahend und vorherige Ausleihe an, während die beiden Ausgaben als Ausleih-O / P und Differenz bezeichnet werden. Das folgende Bild zeigt die Wahrheitstabelle des Vollsubtrahierers.

Eingänge | Ausgänge | |||

Minuend (A) | Subtrahend (B) | Ausleihen (Bin) | Unterschied (D) | Ausleihen (Kampf) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-Karte

Die Vereinfachung der volle Subtrahierer-K-Karte für die oben genannte Differenz und Ausleihe ist unten gezeigt.

Die Gleichungen für die Differenz sowie Bin sind unten aufgeführt.

Der Ausdruck für Unterschied ist:

D = A’B’Bin + AB’Bin’+ A’BBin’ + ABBin

Der Ausdruck für Ausleihen lautet:

Kampf = A’Bin + A’B + BBin

Kaskadierung der vollen Subtrahierschaltung

Zuvor haben wir einen Überblick über diesen ähnlichen Schaltplan mit Logikgattern besprochen. Wenn wir jedoch zwei ansonsten mehr 1-Bit-Zahlen subtrahieren möchten, ist diese Subtrahiererschaltung sehr hilfreich, um einzelne Bitzahlen zu kaskadieren, und subtrahiert auch mehr als zwei Binärzahlen. In solchen Fällen wird eine Volladdierer-Kaskadenschaltung mit Hilfe eines NICHT-Logikgatters verwendet. Die Umwandlung der Schaltung vom Volladdierer zum Vollsubtrahierer kann unter Verwendung der 2-Komplement-Technik erfolgen.

Im Allgemeinen invertieren Sie die Subtrahend-Eingänge für den Volladdierer mit dem NOT-Gatter, ansonsten mit einem Inverter. Durch Hinzufügen dieses Minuends (nicht invertierter Eingang) und Subtrahends (invertierter Eingang) beträgt das LSB (Übertragseingang) der FA-Schaltung 1, was bedeutet, dass die Logik hoch ist, andernfalls subtrahieren wir zwei Binärziffern unter Verwendung der Zweierkomplementtechnik. Die Ausgabe des FA ist das Diff-Bit. Wenn wir die Ausführung invertieren, können wir das MSB erhalten, andernfalls das Borrow-Bit. Tatsächlich können wir die Schaltung so gestalten, dass die Ausgabe beobachtet werden kann.

Verilog-Code

Für den Codierungsteil müssen wir zunächst die strukturelle Art der Modellierung des Logikschaltbilds überprüfen. Das Logikdiagramm hierfür kann unter Verwendung eines UND-Gatters, halber Subtrahiererschaltungen und der Kombination von Logikgattern wie UND-, ODER-, NICHT-XOR-Gattern erstellt werden. Wie bei der Strukturmodellierung erklären wir verschiedene Module für jede grundlegende Elementanordnung. Im folgenden Code können für jedes Gate unterschiedliche Module definiert werden.

Dieses Modul ist für das ODER-Gatter.

EINGANG: a0, b0

AUSGABE: c0

Zuletzt werden wir diese Gate-präzisen Module zu einem einzigen Modul zusammenfassen. Dafür verwenden wir hier die Instanziierung des Moduls. Diese Instanziierung kann jetzt verwendet werden, sobald ein genaues Modul oder eine exakte Funktion für verschiedene Eingabesätze repliziert werden soll. Zuerst entwerfen wir einen halben Subtrahierer, dann wird dieses Modul verwendet, um einen vollständigen Subtrahierer zu implementieren. Um dies zu implementieren, verwenden wir das ODER-Gatter, um die o / ps für die Variable Bout zu kombinieren. Das Verilog-Code für den vollständigen Subtrahierer wird unten gezeigt

Modul or_gate (a0, b0, c0)

Eingabe a0, b0

Ausgang c0

weise c0 = a0 | zu b0

Endmodul

Modul xor_gate (a1, b1, c1)

Eingabe a1, b1

Ausgang c1

weise c1 = a1 ^ b1 zu

Endmodul

Modul and_gate (a2, b2, c2)

Eingabe a2, b2

Ausgang c2

weise c2 = a2 & b2 zu

Endmodul

Modul not_gate (a3, b3)

Eingabe a3

Ausgang b3

weise b3 = ~ a3 zu

Endmodul

Modul half_subtractor (a4, b4, c4, d4)

Eingabe a4, b4

Ausgang c4, d4

Draht x

xor_gate u1 (a4, b4, c4)

und_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

Endmodul

Modul full_subtractor (A, B, Bin, D, Bout)

Eingabe A, B, Bin

Ausgang D, Bout

Draht p, q, r

halber Subtrahierer u4 (A, B, p, q)

halber Subtrahierer u5 (p, Bin, D, r)

or_gate u6 (q, r, Bout)

Endmodul

Vollsubtrahierer mit 4X1 Multiplexer

Die Ausführung der Subtraktion kann durch die Komplementmethode der beiden erfolgen. Daher benötigen wir ein 1-XOR-Gatter, das verwendet wird, um 1-Bit zu invertieren und eins in das Übertragsbit aufzunehmen. Der Ausgang von DIFFERENCE ist ähnlich dem Ausgang SUM in der Volladdiererschaltung, jedoch ist das BARROW o / p nicht dem Übertragsausgang des Volladdierers ähnlich, jedoch ist es invertiert und komplementiert, wie A - B = A + (-B) = A + Zwei-Komplement von B.

Der Aufbau dieses 4X1-Multiplexers ist im folgenden Logikdiagramm dargestellt. Dieser Entwurf kann mit den folgenden Schritten durchgeführt werden.

4X1 Multiplexer

- In Schritt 1 gibt es zwei Ausgänge wie Sub und Borrow. Wir müssen also 2 Multiplexer auswählen.

- In Schritt 2 kann die Wahrheitstabelle zusammen mit K-Maps implementiert werden

- In Schritt 3 können die beiden Variablen als Auswahlzeile ausgewählt werden. Zum Beispiel sind B & C in diesem Fall.

Wahrheitstabelle

Das Wahrheitstabelle des vollen Subtrahierers Die Schaltung, die einen 4X1-Multiplexer verwendet, umfasst Folgendes

ZU | B. | C. | Sub | Leihen |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Voller Subtrahierer mit Decoder

Das Entwerfen eines vollständigen Subtrahierers unter Verwendung von 3-8 Decodern kann unter Verwendung von aktiv niedrigen Ausgängen erfolgen. Nehmen wir an, dass der Decoder anhand des folgenden Logikdiagramms funktioniert. Der Decoder enthält drei Eingänge in 3-8 Decodern. Basierend auf der Wahrheitstabelle können wir die Intervalle für die Ausgaben von Differenz und Ausleihe schreiben.

Aus der obigen Wahrheitstabelle

Für die verschiedenen Funktionen in der Wahrheitstabelle können die Zwischenzeiten als 1,2,4,7 geschrieben werden, und in ähnlicher Weise können für die Ausleihe die Zwischenzeiten als 1,2,3,7 geschrieben werden. Die 3-8 Decoder enthalten drei Eingänge sowie 8 Ausgänge wie 0 bis 7 Zahlen.

3-zu-8-Decoder

Wenn der Eingang des Subtrahierers 000 ist, ist der Ausgang '0' aktiv, und wenn der Eingang 001 ist, ist der Ausgang '1' aktiv.

Jetzt können die Ausgänge des Subtrahierers von 1, 2, 4 und 7 genommen werden, um ihn mit einem NAND-Gatter zu verbinden, dann ist der Ausgang die Differenz. Diese Ausgänge können mit anderen NAND-Logikgattern verbunden werden, bei denen sich der Ausgang zum Ausleihen ändert.

Wenn der Eingang beispielsweise 001 ist, ist der Ausgang 1, was bedeutet, dass er aktiv ist. Der Ausgang ist also aktiv niedrig und der Ausgang kann vom NAND-Gatter erhalten werden, das als Differenzfunktion wie hoch bezeichnet wird, und die Ausleihfunktion ändert sich ebenfalls als hoch. Daher erhalten wir die bevorzugte Ausgabe. Schließlich arbeitet der Decoder wie ein vollständiger Subtrahierer.

Vorteile und Nachteile

Das Vorteile des Subtrahierers das Folgende einschließen.

- Das Design des Subtrahierers ist sowohl sehr einfach als auch zu implementieren

- Leistungsabzug innerhalb von DSP (digitale Signalverarbeitung)

- Rechenaufgaben können mit hoher Geschwindigkeit ausgeführt werden.

Das Nachteile des Subtrahierers das Folgende einschließen.

- Im halben Subtrahierer gibt es keine Bedingung, um leihähnliche Eingaben aus der früheren Phase zu akzeptieren.

- Die Subtrahiergeschwindigkeit kann durch die Verzögerung in der Schaltung partiell sein.

Anwendungen

Einige der Anwendungen des Vollsubtrahierers das Folgende einschließen

- Diese werden im Allgemeinen für ALU (Arithmetic Logic Unit) in Computern verwendet, um als CPU & GPU für die Anwendungen von Grafiken zu subtrahieren, um die Schaltungsschwierigkeiten zu verringern.

- Subtrahierer werden hauptsächlich zur Ausführung von arithmetischen Funktionen wie Subtraktion in elektronischen Taschenrechnern sowie in digitalen Geräten verwendet.

- Diese gelten auch für verschiedene Mikrocontroller für arithmetische Subtraktion, Timer und den Programmzähler (PC)

- Subtrahierer werden in Prozessoren verwendet, um Tabellen, Adressen usw. zu berechnen.

- Es ist auch nützlich für DSP- und netzwerkbasierte Systeme.

- Diese werden hauptsächlich für ALU in Computern zum Subtrahieren wie CPU & GPU für Grafikanwendungen verwendet, um die Komplexität der Schaltung zu verringern.

- Diese werden hauptsächlich verwendet, um arithmetische Funktionen wie Subtraktion innerhalb digitaler Geräte, Taschenrechner usw. auszuführen.

- Diese Subtrahierer eignen sich auch für verschiedene Mikrocontroller für Timer, PC (Programmzähler) und arithmetische Subtraktion

- Diese werden für Prozessoren verwendet, um Adressen, Tabellen usw. zu berechnen.

- Die Implementierung mit Logikgattern wie NAND & NOR kann mit jeder vollständigen Subtrahiererlogikschaltung erfolgen, da beide NOR- und NAND-Gatter als Universalgatter bezeichnet werden.

Aus den obigen Informationen kann man durch Auswerten des Addierers, des vollständigen Subtrahierers unter Verwendung von zwei Halb-Subtrahierer-Schaltungen und seiner tabellarischen Formen feststellen, dass Dout im Vollsubtrahierer dem Sout des Volladdierers genau ähnlich ist. Die einzige Variation besteht darin, dass A (Eingangsvariable) im Vollsubtrahierer ergänzt wird. Somit ist es möglich, die Volladdiererschaltung in einen Vollsubtrahierer umzuwandeln, indem nur das i / p A ergänzt wird, bevor es gegeben wird die Logikgatter um die letzte Ausleihbitausgabe (Bout) zu erzeugen.

Durch Verwendung einer vollständigen Subtrahierer-Logikschaltung können ein vollständiger Subtrahierer unter Verwendung von NAND-Gattern und ein vollständiger Subtrahierer unter Verwendung von Nor-Gattern implementiert werden, da sowohl das NAND- als auch das NOR-Gatter als universelle Gatter behandelt werden. Hier ist eine Frage für Sie, was ist der Unterschied zwischen halbem Subtrahierer und vollem Subtrahierer?