Verschiedene Arten von digitalen Systemen werden aus sehr wenigen Arten grundlegender Netzwerkkonfigurationen wie UND-Gatter, NAND-Gatter oder Or-Gatter usw. aufgebaut. Diese Elementarschaltungen werden immer wieder in verschiedenen topologischen Kombinationen verwendet. Digitale Systeme müssen nicht nur Logik ausführen, sondern auch Binärzahlen speichern. Für diese Speicherzellen auch bekannt als FLIP-FLOP' s sind entworfen. Einige Funktionen wie die binäre Addition ausführen. Um solche Funktionen auszuführen, sind daher Kombinationen von Logikgatter und FLIP-FLOPs werden über einen Single-Chip-IC entworfen. Diese ICs bilden die praktischen Bausteine der digitalen Systeme. Einer dieser Bausteine für die binäre Addition ist der Carry Look-Ahead-Addierer.

Was ist ein Carry Look-Ahead-Addierer?

Ein digitaler Computer muss Schaltungen enthalten, die arithmetische Operationen wie Addition, Subtraktion, Multiplikation und Division ausführen können. Unter diesen sind Addition und Subtraktion die Grundoperationen, während Multiplikation und Division die wiederholte Addition bzw. Subtraktion sind.

Um diese Operationen auszuführen, werden 'Addiererschaltungen' unter Verwendung grundlegender Logikgatter implementiert. Addiererschaltungen wurden als Halbaddierer, Volladdierer, Ripple-Carry-Addierer und Carry Look-Ahead-Addierer entwickelt.

Unter diesen Carry Look-Ahead-Addierern befindet sich die schnellere Addiererschaltung. Es reduziert die Ausbreitungsverzögerung, die während der Addition auftritt, indem komplexere Hardwareschaltungen verwendet werden. Es wird entworfen, indem die Ripple-Carry-Addiererschaltung so transformiert wird, dass die Übertragslogik des Addierers in eine Zwei-Ebenen-Logik geändert wird.

4-Bit-Carry-Look-Ahead-Addierer

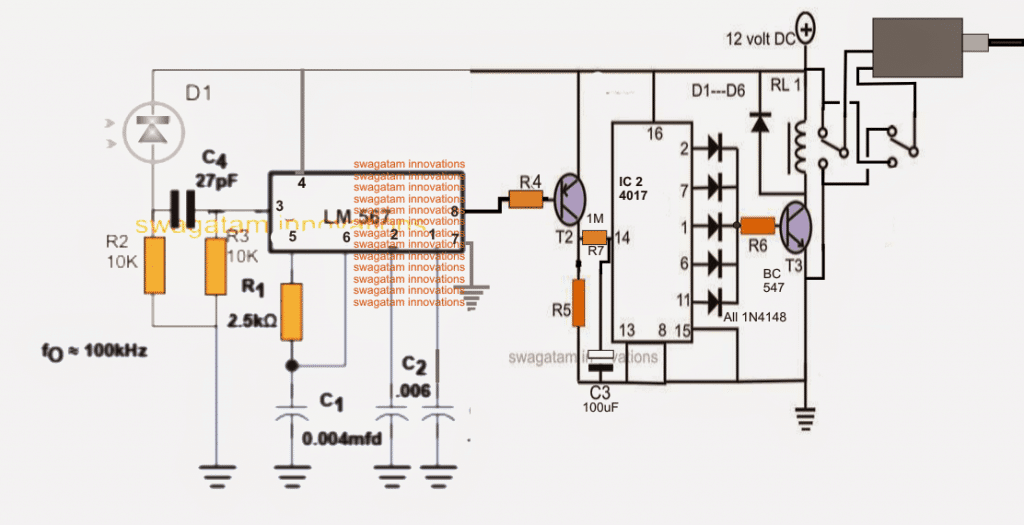

Bei parallelen Addierern wird die Übertragsausgabe jedes Volladdierers als Übertragseingabe in den Zustand nächsthöherer Ordnung gegeben. Daher ist es diesen Addierern nicht möglich, Übertrags- und Summenausgaben eines beliebigen Zustands zu erzeugen, es sei denn, für diesen Zustand ist eine Übertragseingabe verfügbar.

Damit eine Berechnung stattfinden kann, muss die Schaltung warten, bis sich das Übertragsbit in alle Zustände ausbreitet. Dies induziert eine Übertragsausbreitungsverzögerung in der Schaltung.

4-Bit-Ripple-Carry-Adder

Betrachten Sie die obige 4-Bit-Ripple-Carry-Addierer-Schaltung. Hier kann die Summe S3 erzeugt werden, sobald die Eingänge A3 und B3 gegeben sind. Der Übertrag C3 kann jedoch erst berechnet werden, wenn das Übertragsbit C2 angelegt ist, während C2 von C1 abhängt. Um endgültige Ergebnisse im stationären Zustand zu erzielen, muss sich der Übertrag daher in allen Zuständen ausbreiten. Dies erhöht die Übertragsausbreitungsverzögerung der Schaltung.

Die Ausbreitungsverzögerung des Addierers wird berechnet als 'die Ausbreitungsverzögerung jedes Gatters multipliziert mit der Anzahl der Stufen in der Schaltung'. Für die Berechnung einer großen Anzahl von Bits müssen mehr Stufen hinzugefügt werden, was die Verzögerung viel schlimmer macht. Um diese Situation zu lösen, wurde Carry Look-Ahead Adder eingeführt.

Um die Funktionsweise eines Carry Look-Ahead-Addierers zu verstehen, wird im Folgenden ein 4-Bit-Carry Look-Ahead-Addierer beschrieben.

4-Bit-Carry-Look-Ahead-Addierer-Logik-Diagramm

Bei diesem Addierer ist der Übertragseingang in jeder Stufe des Addierers unabhängig von den Übertragsbits, die in den unabhängigen Stufen erzeugt werden. Hier hängt die Ausgabe einer Stufe nur von den Bits ab, die in den vorherigen Stufen hinzugefügt wurden, und von der Übertragseingabe, die in der Anfangsstufe bereitgestellt wurde. Daher muss die Schaltung in keiner Stufe auf die Erzeugung eines Übertragsbits aus der vorherigen Stufe warten, und das Übertragsbit kann zu jedem Zeitpunkt ausgewertet werden.

Wahrheitstabelle des Carry Look-Ahead-Addierers

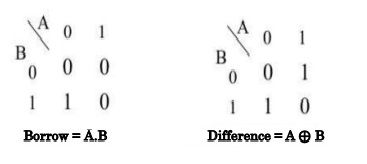

Um die Wahrheitstabelle dieses Addierers abzuleiten, werden zwei neue Begriffe eingeführt - Carry Generate und Carry Propagate. Carry Generiere Gi = 1, wenn ein Carry Ci + 1 generiert wird. Dies hängt von den Eingängen Ai und Bi ab. Gi ist 1, wenn sowohl Ai als auch Bi 1 sind. Daher wird Gi als Gi = Ai berechnet. Bi.

Carry Propagated Pi ist mit der Ausbreitung von Carry von Ci nach Ci + 1 verbunden. Es wird berechnet als Pi = Ai ⊕ Bi. Die Wahrheitstabelle dieses Addierers kann aus der Änderung der Wahrheitstabelle eines Volladdierers abgeleitet werden.

Unter Verwendung der Gi- und Pi-Terme werden die Sum Si und Carry Ci + 1 wie folgt angegeben:

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Daher können die Übertragsbits C1, C2, C3 und C4 als berechnet werden

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Aus den Gleichungen kann beobachtet werden, dass der Übertrag Ci + 1 nur vom Übertrag C0 abhängt, nicht von den Zwischenübertragsbits.

Carry-Look-Ahead-Adder-Wahrheitstabelle

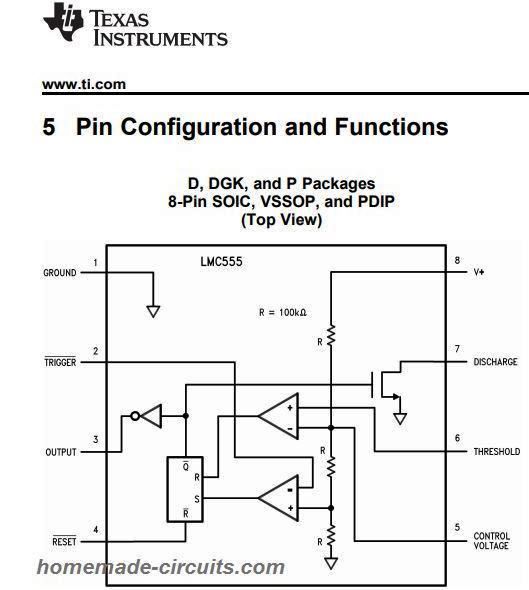

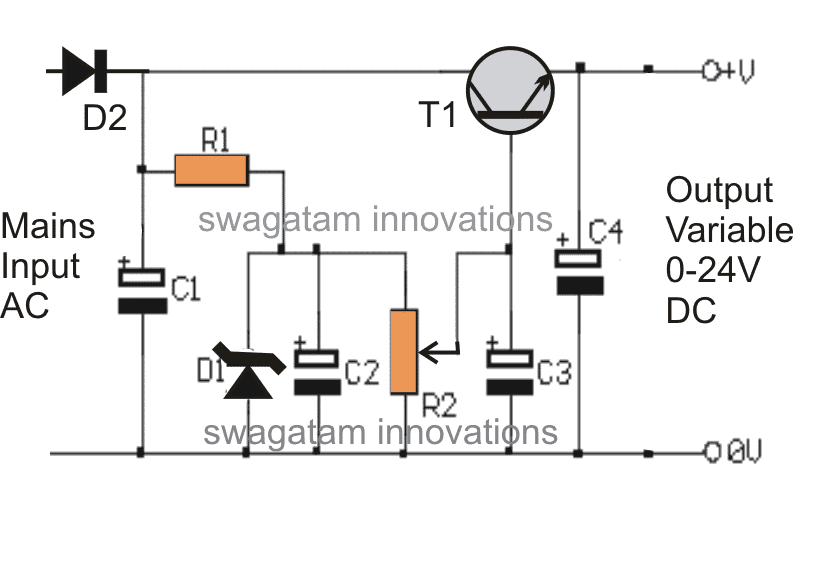

Schaltplan

Die obigen Gleichungen werden unter Verwendung von Kombinationsschaltungen mit zwei Ebenen zusammen mit UND- oder ODER-Gattern implementiert, wobei angenommen wird, dass Gatter mehrere Eingänge haben.

Carry-Output-Generation-Circuit-of-Carry-Look-Ahead-Addierer

Die Carry Look-Ahead-Addiererschaltung für 4-Bit ist unten angegeben.

4-Bit-Carry-Look-Ahead-Addierer-Schaltplan

8-Bit- und 16-Bit-Carry-Look-Ahead-Addiererschaltungen können durch Kaskadieren der 4-Bit-Addiererschaltung mit Übertragslogik entworfen werden.

Vorteile von Carry Look-Ahead Adder

Bei diesem Addierer wird die Ausbreitungsverzögerung verringert. Die Übertragsausgabe in jeder Stufe hängt nur vom anfänglichen Übertragsbit der Anfangsstufe ab. Mit diesem Addierer können die Zwischenergebnisse berechnet werden. Dieser Addierer ist der schnellste Addierer, der für die Berechnung verwendet wird.

Anwendungen

Hochgeschwindigkeits-Carry-Look-Ahead-Addierer werden so implementiert wie ICs. Daher ist es einfach, den Addierer in Schaltungen einzubetten. Durch Kombinieren von zwei oder mehr Addierern können Berechnungen von Booleschen Funktionen mit höherem Bit leicht durchgeführt werden. Hier ist die Zunahme der Anzahl von Gattern auch moderat, wenn sie für höhere Bits verwendet wird.

Für diesen Addierer gibt es einen Kompromiss zwischen Fläche und Geschwindigkeit. Wenn es für Berechnungen mit höheren Bits verwendet wird, liefert es eine hohe Geschwindigkeit, aber die Komplexität der Schaltung wird auch erhöht, wodurch die von der Schaltung eingenommene Fläche vergrößert wird. Dieser Addierer wird normalerweise als 4-Bit-Module implementiert, die bei Verwendung für höhere Berechnungen zusammen kaskadiert werden. Dieser Addierer ist im Vergleich zu anderen Addierern teurer.

Für die boolesche Berechnung in Computern werden regelmäßig Addierer verwendet. Charles Babbage implementierte einen Mechanismus zum Antizipieren des Übertragsbits in Computern, um die durch die Ripple-Carry-Addierer . Beim Entwurf eines Systems ist die Rechengeschwindigkeit der entscheidende Faktor für einen Designer. 1957 patentierte Gerald B. Rosenberger den modernen Binary Carry Look-Ahead-Addierer. Basierend auf der Analyse der Gate-Verzögerung und der Simulation werden Experimente durchgeführt, um die Schaltung dieses Addierers zu modifizieren, um ihn noch schneller zu machen. Was ist für einen n-Bit-Carry-Look-Ahead-Addierer die Ausbreitungsverzögerung, wenn eine Verzögerung jedes Gatters 20 beträgt?

Bildnachweis