Der Metalloxid-Halbleitertransistor oder MOS-Transistor ist ein grundlegender Baustein in Logikchips, Prozessoren und modernen digitalen Speichern. Es ist ein Mehrheitsträgergerät, bei dem der Strom in einem leitenden Kanal zwischen Source und Drain durch eine an das Gate angelegte Spannung moduliert wird. Dieser MOS-Transistor spielt eine Schlüsselrolle in verschiedenen Analog- und Mixed-Signal-ICs. Dieser Transistor ist ziemlich anpassungsfähig, fungiert also als Verstärker, Schalter oder a Widerstand . nicht Transistoren werden in zwei Typen PMOS & NMOS eingeteilt. Daher behandelt dieser Artikel einen Überblick über NMOS-Transistor – Herstellung, Schaltung & Funktion.

Was ist ein NMOS-Transistor?

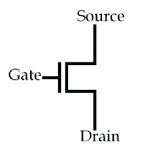

Ein NMOS-(n-Kanal-Metalloxid-Halbleiter)-Transistor ist ein Transistortyp, bei dem n-Typ-Dotierstoffe in dem Gate-Bereich verwendet werden. Eine positive (+ve) Spannung am Gate-Anschluss schaltet das Gerät ein. Dieser Transistor wird hauptsächlich in verwendet CMOS (komplementärer Metalloxid-Halbleiter) und auch in Logik- und Speicherchips. Im Vergleich zum PMOS-Transistor ist dieser Transistor sehr schnell, sodass mehr Transistoren auf einem einzigen Chip untergebracht werden können. Das NMOS-Transistorsymbol ist unten dargestellt.

Wie funktioniert ein NMOS-Transistor?

Die Arbeitsweise des NMOS-Transistors ist; Wenn der NMOS-Transistor eine nicht vernachlässigbare Spannung empfängt, bildet er einen geschlossenen Stromkreis, was bedeutet, dass die Verbindung vom Source-Anschluss zum Drain als Draht funktioniert. Der Strom fließt also vom Gate-Anschluss zur Source. Wenn dieser Transistor eine Spannung von etwa 0 V empfängt, bildet er in ähnlicher Weise einen offenen Stromkreis, was bedeutet, dass die Verbindung vom Source-Anschluss zum Drain unterbrochen wird, sodass Strom vom Gate-Anschluss zum Drain fließt.

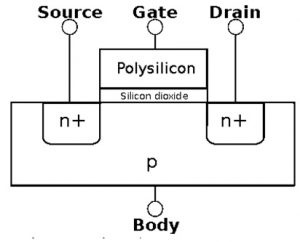

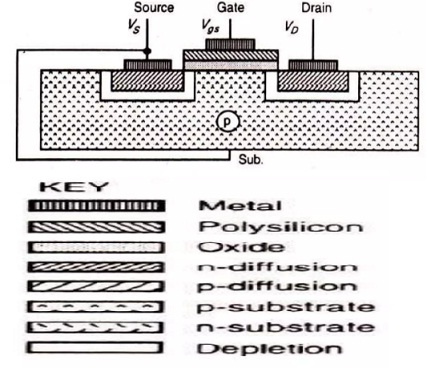

Querschnitt des NMOS-Transistors

Im Allgemeinen wird ein NMOS-Transistor einfach mit einem p-Typ-Körper aus zwei n-Typ-Halbleiterregionen aufgebaut, die neben dem als Source und Drain bekannten Gate liegen. Dieser Transistor hat ein steuerndes Gate, das den Elektronenfluss zwischen den Source- und Drain-Anschlüssen steuert.

Da bei diesem Transistor der Körper des Transistors geerdet ist, sind die PN-Übergänge von Source und Drain zum Körper hin in Sperrichtung vorgespannt. Wenn die Spannung am Gate-Anschluss erhöht wird, beginnt ein elektrisches Feld zu wachsen und zieht freie Elektronen an die Basis der Si-SiO2-Grenzfläche.

Sobald die Spannung hoch genug ist, füllen Elektronen alle Löcher und ein dünner Bereich unter dem Gate, der als Kanal bekannt ist, wird invertiert, um als Halbleiter vom n-Typ zu fungieren. Dadurch wird eine leitende Spur vom Source-Anschluss zum Drain erzeugt, indem der Stromfluss ermöglicht wird, sodass der Transistor eingeschaltet wird. Wenn der Gate-Anschluss geerdet ist, fließt kein Strom in den in Sperrichtung vorgespannten Übergang, sodass der Transistor ausgeschaltet wird.

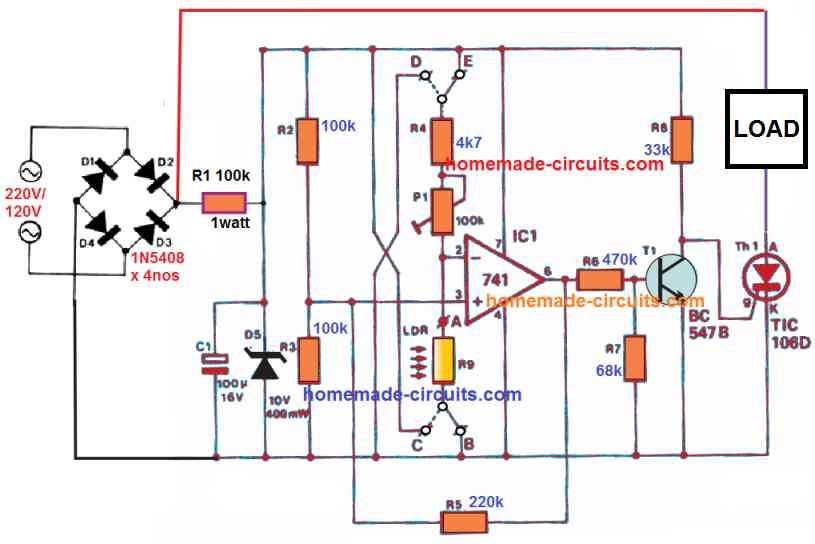

NMOS-Transistorschaltung

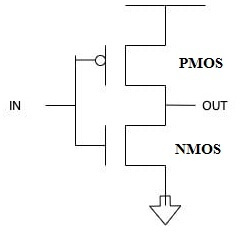

Das NOT-Gate-Design mit PMOS- und NMOS-Transistoren ist unten dargestellt. Um ein NICHT-Gatter zu entwerfen, müssen wir pMOS- und nMOS-Transistoren kombinieren, indem wir einen pMOS-Transistor mit der Source und einen nMOS-Transistor mit Masse verbinden. Die Schaltung wird also unser erstes CMOS-Transistorbeispiel sein.

Das NICHT-Gatter ist eine Art von Logikgatter, das einen invertierten Eingang als Ausgang erzeugt. Dieses Gatter wird auch Inverter genannt. Wenn der Eingang „0“ ist, ist der invertierte Ausgang „1“.

Wenn der Eingang Null ist, geht er zum pMOS-Transistor oben und zum nMOS-Transistor unten. Sobald der Eingangswert „0“ den pMOS-Transistor erreicht, wird er in „1“ invertiert. somit wird die Verbindung zur Quelle gestoppt. Dies erzeugt also einen logischen „1“-Wert, wenn die Verbindung zum Drain (GND) ebenfalls geschlossen ist. Wir wissen, dass der nMOS-Transistor den Eingangswert nicht invertiert, daher nimmt er den Wert Null unverändert an und stellt einen offenen Stromkreis zum Drain her. Für das Gate wird also ein logischer Eins-Wert erzeugt.

Wenn der Eingangswert „1“ ist, wird dieser Wert in ähnlicher Weise an beide Transistoren in der obigen Schaltung gesendet. Sobald der Wert „1“ den pMOS-Transistor empfängt, wird er zu einem „o“ invertiert. dadurch ist die Verbindung zur Quelle offen. Sobald der nMOS-Transistor den Wert „1“ erhält, wird er nicht invertiert. Der Eingabewert bleibt also Eins. Sobald ein Wert vom nMOS-Transistor empfangen wird, wird die Verbindung zum GND geschlossen. Es wird also eine logische „0“ als Ausgang erzeugt.

Herstellungsprozess

Der Herstellungsprozess für NMOS-Transistoren umfasst viele Schritte. Derselbe Prozess kann für PMOS- und CMOS-Transistoren verwendet werden. Das am häufigsten verwendete Material bei dieser Herstellung ist entweder Polysilizium oder Metall. Die Schritt-für-Schritt-Fertigungsprozessschritte des NMOS-Transistors werden unten diskutiert.

Schritt 1:

Eine dünne Siliziumwaferschicht wird durch einfaches Dotieren mit Bormaterial in P-Typ-Material umgewandelt.

Schritt 2:

Auf einem kompletten p-Substrat wird eine dicke SiO2-Schicht aufgewachsen

Schritt 3:

Nun wird die Oberfläche durch einen Fotolack auf die dicke Sio2-Schicht aufgetragen.

Schritt 4:

Anschließend wird diese Schicht mit UV-Licht mit einer Maske belichtet, die diejenigen Bereiche beschreibt, in die gemeinsam mit Transistorkanälen diffundiert werden soll.

Schritt 5:

Diese Bereiche werden gemeinsam mit dem darunter liegenden SiO2 weggeätzt, sodass die Oberfläche des Wafers innerhalb des durch die Maske definierten Fensters freigelegt wird.

Schritt 6:

Der restliche Fotolack wird abgetrennt und eine dünne Sio2-Schicht wird typischerweise 0,1 Mikrometer über die gesamte Fläche des Chips gezüchtet. Als nächstes wird darauf Polysilizium angeordnet, um die Gate-Struktur zu bilden. Ein Fotolack wird auf die gesamte Polysiliziumschicht aufgebracht und bestrahlt die gesamte Maske2 mit ultraviolettem Licht.

Schritt 7:

Durch Erhitzen des Wafers auf die maximale Temperatur werden Diffusionen erreicht und Gas mit gewünschten n-Typ-Verunreinigungen wie Phosphor durchgelassen.

Schritt8:

Überall wird Siliziumdioxid mit einer Dicke von einem Mikrometer aufgewachsen und Photoresistmaterial wird darauf aufgebracht. Setzen Sie das ultraviolette Licht (UV) durch die Maske 3 auf die bevorzugten Gate-, Source- und Drain-Bereiche, die geätzt werden, um die Kontaktschnitte vorzunehmen.

Schritt 9:

Jetzt wird ein Metall wie Aluminium über seine einen Mikrometer breite Oberfläche gelegt. Noch einmal wird ein Fotolackmaterial über das gesamte Metall gezüchtet und UV-Licht durch die Maske 4 ausgesetzt, die eine geätzte Form für das obligatorische Verbindungsdesign ist. Die endgültige NMOS-Struktur ist unten gezeigt.

PMOS gegen NMOS-Transistor

Der Unterschied zwischen PMOS- und NMOS-Transistoren wird unten diskutiert.

| PMOS-Transistor | NMOS-Transistor |

| PMOS-Transistor steht für P-Kanal-Metalloxid-Halbleiter-Transistor. | NMOS-Transistor steht für N-Kanal-Metalloxid-Halbleiter-Transistor. |

| Source und Drain in PMOS-Transistoren werden einfach mit Halbleitern vom n-Typ hergestellt | Die Source und der Drain im NMOS-Transistor werden einfach mit Halbleitern vom p-Typ hergestellt. |

| Das Substrat dieses Transistors besteht aus einem Halbleiter vom n-Typ | Das Substrat dieses Transistors besteht aus einem Halbleiter vom p-Typ |

| Die Mehrzahl der Ladungsträger in PMOS sind Löcher. | Die Mehrzahl der Ladungsträger in NMOS sind Elektronen. |

| Im Vergleich zu NMOS sind PMOS-Geräte nicht kleiner. | NMOS-Geräte sind im Vergleich zu PMOS-Geräten ziemlich kleiner. |

| PMOS-Geräte können im Vergleich zu NMOS-Geräten nicht schneller geschaltet werden. | Im Vergleich zu PMOS-Bauelementen können NMOS-Bauelemente schneller geschaltet werden. |

| Der PMOS-Transistor leitet, sobald eine niedrige Spannung an das Gate angelegt wird. | Der NMOS-Transistor leitet, sobald eine hohe Spannung an das Gate angelegt wird. |

| Diese sind störanfälliger. | Im Vergleich zu PMOS sind diese nicht immun gegen Rauschen. |

| Die Schwellenspannung (Vth) dieses Transistors ist eine negative Größe. | Die Schwellenspannung (Vth) dieses Transistors ist eine positive Größe. |

Eigenschaften

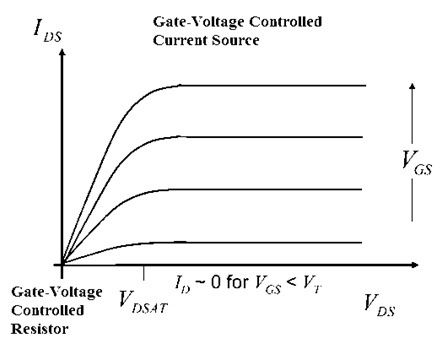

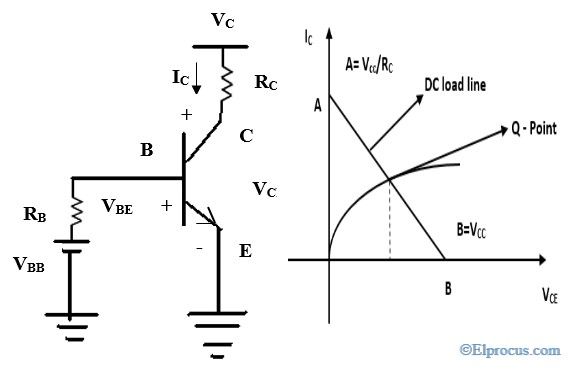

Das I-V-Eigenschaften des NMOS-Transistors sind unten gezeigt. Die Spannung zwischen den Gate- und den Source-Anschlüssen „V GS ’ & auch zwischen Source & Drain ‘V DS ’. Also die Kurven zwischen I DS und v DS werden erreicht, indem einfach der Anschluss der Quelle geerdet, ein anfänglicher VGS-Wert eingestellt und V gewobbelt wird DS von „0“ bis zum höchsten DC-Spannungswert, der von V angegeben wird DD beim Treten des V GS Wert von „0“ bis V DD . Also für extrem niedrige V GS , das i DS sind extrem klein und haben einen linearen Trend. Als das v GS Wert wird hoch, dann I DS verbessert & wird die folgende Abhängigkeit von V haben GS & IN DS ;

Wenn v GS kleiner oder gleich V ist TH , dann ist der Transistor im AUS-Zustand und verhält sich wie ein offener Stromkreis.

Wenn v GS ist größer als V TH , dann gibt es zwei Betriebsarten.

Wenn v DS ist kleiner als V GS - IN TH , dann arbeitet der Transistor im linearen Modus und fungiert als Widerstand (R AN ).

IDS = u eff C Ochse W/L [(V GS - IN TH )IN DS – ½ V DS ^2]

Woher,

„µeff“ ist die effektive Beweglichkeit des Ladungsträgers.

„COX“ ist die Kapazität des Gateoxids für jede Flächeneinheit.

W & L sind die Breite und Länge des Kanals entsprechend. Das R AN Wert wird einfach durch die Spannung des Gates gesteuert, folgt wie folgt;

R EIN = 1 in n C Ochse W/L [(V GS - IN TH )IN DS – ½ V DS ^2]

Wenn VDS größer oder gleich V ist GS - IN TH , dann arbeitet der Transistor im Sättigungsmodus

ich DS = u n C Ochse W/L [(V GS - IN TH )^2 (1+λ V DS ]

In dieser Region, wenn ich DS höher ist, dann ist der Strom minimal von V abhängig DS Der höchste Wert wird jedoch einfach über VGS gesteuert. Die Kanallängenmodulation „λ“ erklärt die Erhöhung innerhalb von IDS durch eine Erhöhung innerhalb von VDS in Transistoren aufgrund von Abschnürungen. Diese Abschnürung tritt auf, sobald sowohl V DS und v GS entscheiden über das elektrische Feldmuster in der Nähe des Drain-Bereichs und ändern so die Richtung der natürlichen Versorgungsladungsträger. Dieser Effekt verkürzt die Länge des effizienten Kanals und erhöht I DS . Idealerweise ist „λ“ äquivalent zu „0“, sodass I DS ist völlig unabhängig von V DS Wert innerhalb des Sättigungsbereichs.

Es geht also um alles eine Übersicht über ein NMOS Transistor – Herstellung und Schaltung mit Funktion. Der NMOS-Transistor spielt eine Schlüsselrolle bei der Implementierung von Logikgattern sowie anderen unterschiedlichen digitalen Schaltungen. Dies ist eine mikroelektronische Schaltung, die hauptsächlich beim Entwurf von Logikschaltungen, Speicherchips und im CMOS-Design verwendet wird. Die beliebtesten Anwendungen von NMOS-Transistoren sind Schalter und Spannungsverstärker. Hier ist eine Frage an Sie: Was ist ein PMOS-Transistor?

![12-V-Batterieladekreise [mit LM317, LM338, L200, Transistoren]](https://electronics.jf-parede.pt/img/battery-chargers/11/12v-battery-charger-circuits-using-lm317.png)

![Berührungslose Wechselstrom-Phasendetektorschaltung [Getestet]](https://electronics.jf-parede.pt/img/sensors-detectors/38/non-contact-ac-phase-detector-circuit.png)