Befehlssatz oder Befehlssatzarchitektur ist die Struktur des Computers, die dem Computer Befehle zur Führung des Computers für die Verarbeitung der Datenmanipulation bereitstellt. Der Befehlssatz besteht aus Befehlen, Adressierungsmodi, nativen Datentypen, Registern, Interrupt, Ausnahmebehandlung und Speicherarchitektur. Der Befehlssatz kann mithilfe eines Interpreters in die Software emuliert oder in die Hardware des Prozessors integriert werden. Die Befehlssatzarchitektur kann als Grenze zwischen Software und Hardware betrachtet werden. Klassifizierung von Mikrocontrollern und Mikroprozessoren können basierend auf der RISC- und CISC-Befehlssatzarchitektur ausgeführt werden.

Befehlssatz des Prozessors

Der Befehlssatz gibt die Prozessorfunktionalität an, einschließlich der vom Prozessor unterstützten Operationen, der Speichermechanismen des Prozessors und der Art und Weise, wie die Programme für den Prozessor kompiliert werden.

Was ist RISC und CISC?

Das RISC und CISC kann wie folgt erweitert werden:

RISC repräsentiert den Computer mit reduziertem Befehlssatz und

CISC repräsentiert den Complex Instruction Set Computer.

RISC-Architektur (Reduced Instruction Set Computer)

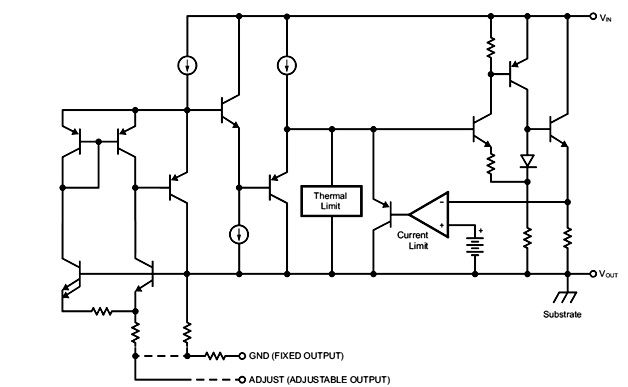

RISC-Architektur

Das Mikrocontroller-Architektur Dieser kleine und hochoptimierte Befehlssatz wird als reduzierter Befehlssatzcomputer oder einfach als RISC bezeichnet. Es wird auch als LOAD / STORE-Architektur bezeichnet.

In den späten 1970er und frühen 1980er Jahren wurden RISC-Projekte hauptsächlich von Stanford, UC-Berkley und IBM entwickelt. Das John Coke vom IBM-Forschungsteam entwickelte RISC, indem es die Anzahl der Anweisungen reduzierte, die für die schnellere Verarbeitung von Berechnungen erforderlich sind als das CISC. Die RISC-Architektur ist schneller und die für die Herstellung der RISC-Architektur erforderlichen Chips sind im Vergleich zur CISC-Architektur auch kostengünstiger.

Typische Merkmale der RISC-Architektur

- Die Pipelining-Technik von RISC führt mehrere Teile oder Stufen von Befehlen gleichzeitig aus, so dass jeder Befehl auf der CPU optimiert wird. Daher haben die RISC-Prozessoren Takt pro Befehl eines Zyklus, und dies wird als Ausführung eines Zyklus bezeichnet.

- Es optimiert die Verwendung des Registers Mit mehr Registern im RISC und mehr Interaktionen im Speicher kann verhindert werden.

- Einfache Adressierungsmodi und sogar komplexe Adressierungen können mithilfe von Arithmetik durchgeführt werden UND / ODER logische Operationen .

- Es vereinfacht das Compiler-Design, indem identische Allzweckregister verwendet werden, wodurch jedes Register in jedem Kontext verwendet werden kann.

- Für eine effiziente Nutzung der Register und eine Optimierung der Pipelining-Anwendungen ist ein reduzierter Befehlssatz erforderlich.

- Die Anzahl der für den Opcode verwendeten Bits wird reduziert.

- Im Allgemeinen gibt es 32 oder mehr Register im RISC.

Vorteile der RISC-Prozessorarchitektur

- Aufgrund der kleinen Anweisungen von RISC können Hochsprachen-Compiler effizienteren Code erstellen.

- RISC ermöglicht die freie Nutzung des Speicherplatzes Mikroprozessoren wegen seiner Einfachheit.

- Anstatt Stack zu verwenden, verwenden viele RISC-Prozessoren die Register, um Argumente zu übergeben und die lokalen Variablen zu speichern.

- RISC-Funktionen verwenden nur wenige Parameter, und die RISC-Prozessoren können die Aufrufanweisungen nicht verwenden. Verwenden Sie daher Anweisungen mit fester Länge, die einfach zu leiten sind.

- Die Geschwindigkeit der Operation kann maximiert und die Ausführungszeit minimiert werden.

- Es werden sehr wenig Anweisungsformate (weniger als vier), einige Anweisungen (ungefähr 150) und einige Adressierungsmodi (weniger als vier) benötigt.

Nachteile der RISC-Prozessorarchitektur

- Mit zunehmender Länge der Befehle steigt die Komplexität, die die RISC-Prozessoren aufgrund ihres Zeichenzyklus pro Befehl ausführen müssen.

- Die Leistung der RISC-Prozessoren hängt hauptsächlich vom Compiler oder Programmierer ab, da das Wissen des Compilers beim Konvertieren des CISC-Codes in einen RISC-Code eine wichtige Rolle spielt. Daher hängt die Qualität des generierten Codes vom Compiler ab.

- Durch das Umplanen des CISC-Codes in einen RISC-Code, der als Code-Erweiterung bezeichnet wird, wird die Größe erhöht. Die Qualität dieser Codeerweiterung hängt wiederum vom Compiler und auch vom Befehlssatz des Computers ab.

- Der Cache der ersten Ebene der RISC-Prozessoren ist auch ein Nachteil des RISC, bei dem diese Prozessoren große Speichercaches auf dem Chip selbst haben. Für die Fütterung der Anweisungen benötigen sie sehr schnelle Speichersysteme .

CISC-Architektur (Complex Instruction Set Computer)

Die Hauptabsicht der CISC-Prozessorarchitektur besteht darin, die Aufgabe durch die Verwendung einer geringeren Anzahl von Montagelinien abzuschließen. Zu diesem Zweck ist der Prozessor so aufgebaut, dass er eine Reihe von Operationen ausführt. Komplexe Anweisungen werden auch als MULT bezeichnet, das funktioniert Speicherbänke eines Computers direkt, ohne dass der Compiler Speicher- und Ladefunktionen ausführt.

CISC-Architektur

Merkmale der CISC-Architektur

- Um die Computerarchitektur zu vereinfachen, unterstützt CISC die Mikroprogrammierung.

- CISC verfügt über eine größere Anzahl vordefinierter Anweisungen, wodurch Hochsprachen einfach zu entwerfen und zu implementieren sind.

- CISC besteht aus weniger Registern und mehr Adressierungsmodi, im Allgemeinen 5 bis 20.

- Der CISC-Prozessor benötigt eine unterschiedliche Zykluszeit für die Ausführung von Anweisungen - Mehrtaktzyklen.

- Aufgrund des komplexen Befehlssatzes des CISC ist die Pipelining-Technik sehr schwierig.

- CISC besteht aus mehr Anweisungen, im Allgemeinen von 100 bis 250.

- Spezielle Anweisungen werden sehr selten verwendet.

- Operanden im Speicher werden durch Anweisungen manipuliert.

Vorteile der CISC-Architektur

- Jeder Maschinensprachenbefehl wird zu einem Mikrocodebefehl gruppiert und entsprechend ausgeführt und dann im Speicher des Hauptprozessors gespeichert, der als Mikrocodeimplementierung bezeichnet wird.

- Da der Mikrocode-Speicher schneller als der Hauptspeicher ist, kann der Mikrocode-Befehlssatz ohne wesentliche Geschwindigkeitsreduzierung gegenüber einer fest verdrahteten Implementierung implementiert werden.

- Der gesamte neue Befehlssatz kann durch Ändern des Mikroprogrammdesigns verarbeitet werden.

- CISC kann die Anzahl der Befehle, die zum Implementieren eines Programms erforderlich sind, durch Erstellen umfangreicher Befehlssätze reduziert und auch dazu gebracht werden, den langsamen Hauptspeicher effizienter zu nutzen.

- Aufgrund der Obermenge von Anweisungen, die aus allen früheren Anweisungen besteht, erleichtert dies die Mikrocodierung.

Nachteile von CISC

- Die von verschiedenen Anweisungen benötigte Taktzeit ist unterschiedlich - aus diesem Grund verlangsamt sich die Leistung der Maschine.

- Die Komplexität des Befehlssatzes und die Chiphardware nehmen zu, da jede neue Version des Prozessors aus einer Teilmenge früherer Generationen besteht.

- Nur 20% der vorhandenen Anweisungen werden in einem typischen Programmierereignis verwendet, obwohl es viele spezielle Anweisungen gibt, die nicht einmal häufig verwendet werden.

- Die Bedingungscodes werden von den CISC-Befehlen als Nebeneffekt jedes Befehls festgelegt, der Zeit für diese Einstellung benötigt - und wenn der nachfolgende Befehl die Bedingungscodebits ändert -, muss der Compiler die Bedingungscodebits untersuchen, bevor dies geschieht.

RISC Vs. CISC

- Die Verschwendungszyklen können vom Programmierer verhindert werden, indem der unnötige Code im RISC entfernt wird. Bei Verwendung des CISC-Codes kommt es jedoch aufgrund der Ineffizienz des CISC zu Verschwendungszyklen.

- In RISC soll jede Anweisung eine kleine Aufgabe ausführen, so dass zur Ausführung einer komplexen Aufgabe mehrere kleine Anweisungen zusammen verwendet werden, während nur wenige Anweisungen erforderlich sind, um dieselbe Aufgabe mit CISC auszuführen - da sie komplexe Aufgaben ausführen kann da die Anweisungen einem hochsprachigen Code ähnlich sind.

- CISC wird normalerweise für Computer verwendet, während RISC für Smartphones, Tablets und andere elektronische Geräte verwendet wird.

Die folgende Abbildung zeigt weitere Unterschiede zwischen RISC und CISC

RISC Vs. CISC

In diesem Artikel werden daher die Vor- und Nachteile der RISC- und CISC-Prozessorarchitektur sowie die Unterschiede zwischen den RISC- und CISC-Architekturen sowie die Unterschiede zwischen den RISC- und CISC-Architekturen anhand einer kurzen Idee erläutert. Für weitere Informationen zu den RISC- und CISC-Architekturen senden Sie bitte Ihre Fragen, indem Sie unten einen Kommentar abgeben.

Bildnachweis:

- Befehlssatz des Prozessors von arstechnica

- RISC-Architektur von lsi-Wettbewerb

- RISC vs. CISC von Zuordnung