Die Umwandlung von Binär in Dezimal kann unter Verwendung eines Geräts, nämlich eines Decoders, erfolgen. Dieses Gerät ist eine Art von kombinatorischer Logikschaltung, die die n-Eingangsleitungen verwendet, um 2n Ausgangsleitungen zu erzeugen. Hier kann die Ausgabe dieses Geräts unter 2n Zeilen liegen. Es gibt verschiedene Arten von Binärdecodern, die mehrere Eingänge sowie mehrere Ausgänge enthalten. Einige Arten von Decodern enthalten einen oder mehrere Freigabeeingänge zusammen mit den Dateneingängen. Immer wenn der Freigabeeingang deaktiviert ist, werden alle Ausgänge deaktiviert. Aufgrund seiner Funktion ändert ein Binärdecoder die Daten von n Eingangssignalen in 2n Ausgangssignale. Bei einigen Arten von Decodern haben sie weniger als 2n Ausgangsleitungen. In dieser Situation kann mindestens ein Ausgabeprototyp für verschiedene Eingabewerte wiederholt werden. Es gibt zwei Arten von Decodern höherer Ordnung, wie 3-Zeilen- bis 8-Zeilen-Decoder und 4-Zeilen- bis 16-Zeilen-Decoder. Dieser Artikel beschreibt eine Übersicht über den 3-Zeilen- bis 8-Zeilen-Decoder.

Was ist ein Decoder?

Ein Decoder ist ein kombinatorische Logikschaltung Dies wird verwendet, um den Code in eine Reihe von Signalen zu ändern. Es ist der umgekehrte Vorgang eines Encoders. Eine Decoderschaltung nimmt mehrere Eingänge und gibt mehrere Ausgänge. Eine Decoderschaltung nimmt Binärdaten von 'n'-Eingängen in einen' 2 ^ n'-eindeutigen Ausgang auf. Zusätzlich zu den Eingangspins verfügt der Decoder über einen Freigabepin. Dies ermöglicht es dem Pin, wenn er negiert wird, die Schaltung inaktiv zu machen. In diesem Artikel diskutieren wir 3 bis 8 Zeilen Decoder und Demultiplexer.

Das Folgende ist die Wahrheitstabelle für einen einfachen 1 bis 2-Zeilen-Decoder, wobei A der Eingang und D0 und D1 die Ausgänge sind.

1 bis 2 Decoder

Die Schaltung zeigt die 1 bis 2-Decoderlogik.

1 bis 2 Decoderschaltung

Ein Demultiplexer ist ein Gerät, das einen einzelnen Eingang nimmt und eine der mehreren Ausgangsleitungen gibt. Ein Demultiplexer nimmt eine einzelne Eingangsdaten und wählt dann einzeln eine der einzelnen Ausgangsleitungen aus. Es ist der umgekehrter Prozess eines Multiplexers . Es wird auch als DEMUX oder Datenverteiler bezeichnet. Ein DEMUX wandelt die serielle Eingangsdatenleitung in parallele Ausgangsdaten um. Ein DEMUX liefert 2n Ausgänge für n Auswahlzeilen mit einem einzigen Eingang.

Demux

DEMUX wird verwendet, wenn die Schaltung das Datensignal an eines der vielen Geräte senden möchte. Ein Decoder wird verwendet, um unter vielen Geräten auszuwählen, während ein Demultiplexer verwendet wird, um das Signal an viele Geräte zu senden.

Das Folgende ist die Wahrheitstabelle für 1 bis 2 Demultiplexer mit 'I' als Eingangsdaten, D0 und D1 sind die Ausgangsdatenleitung und A ist die Auswahlleitung.

1 bis 2 Demux Truth Table

Die Schaltung zeigt das 1 bis 2 Demultiplexer-Schema.

1 bis 2 Demux

Warum brauchen wir einen Decoder?

Die Hauptfunktion eines Decoders besteht darin, einen Code in einen Satz von Signalen umzuwandeln, da er einem Encoder entgegengesetzt ist, aber das Entwerfen von Decodern ist einfach. Der Hauptunterschied zwischen einem Decoder und einem Demultiplexer ist eine Kombinationsschaltung, die verwendet wird, um nur einen Eingang zuzulassen und ihn in einen der Ausgänge zu leiten, während ein Decoder mehrere Eingänge zulässt und den decodierten Ausgang erzeugt.

Entwurfsschritte für 3-Zeilen- bis 8-Zeilen-Decoder

Hier ist der 3-Zeilen- bis 8-Zeilen-Decoder ein Decoder höherer Ordnung, der mit zwei Decodern niedriger Ordnung wie 2-Zeilen- bis 4-Zeilen-Decodern ausgelegt ist. Bevor wir diesen Decoder implementieren, haben wir einen 2-Zeilen- bis 4-Zeilen-Decoder entwickelt.

2 Line to 4 Line Decoder

Dieser 2-Zeilen-4-Zeilen-Decoder enthält zwei Eingänge wie A0 & A1 & 4 Ausgänge wie Y0 bis Y4. Das Blockschaltbild dieses Decoders ist unten dargestellt.

2 Line to 4 Line Decoder

Wenn die Eingänge und die Freigabe 1 sind, ist der Ausgang 1. Hier ist die Wahrheitstabelle des 2 bis 4-Decoders.

IS | A1 | A0 | Y3 | Y2 | Y1 | Y0 |

0 | x | x | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

Der boolesche Ausdruck für jede Ausgabe lautet

Y3 = E. A1. A0

Y2 = E. A1. A0 ′

Y1 = E. A1 '. A0

Y0 = E. A1 '. A0 ′

Jeder Ausgang dieses Decoders enthält einen Produktbegriff. So können die vier Produktterme durch 4 UND-Gatter implementiert werden, wobei jedes Gatter 3 Eingänge sowie 2 Inverter enthält. Das 2 bis 4-Decoder-Logikdiagramm ist unten gezeigt. Somit ist der Ausgang dieses Decoders nichts anderes als die Zwischenzeiten der Eingänge und der Freigabe gleich 1. Wenn die Freigabe Null ist, sind danach alle Ausgänge des Decoders gleich Null. Ebenso erzeugt ein Decoder mit 3 bis 8 Zeilen acht Intervalle für 3 Eingangsvariablen von A0, A1 und A2.

Logikdiagramm von 2 bis 4 Decodern

Implementierung eines 3-Zeilen- bis 8-Zeilen-Decoders

Die Implementierung dieses 3-Zeilen- bis 8-Zeilen-Decoders kann unter Verwendung von zwei 2-Zeilen- bis 4-Zeilen-Decodern erfolgen. Wir haben oben diskutiert, dass ein 2 bis 4-Zeilen-Decoder zwei Eingänge und vier Ausgänge enthält. In 3-Zeilen- bis 8-Zeilen-Decodern enthält es drei Eingänge wie A2, A1 und A0 sowie 8 Ausgänge von Y7 - Y0.

Die folgende Formel wird verwendet, um Implementierung von Decodern höherer Ordnung mit Hilfe von Decodern niedriger Ordnung

Die Anzahl der erforderlichen Decoder niedrigerer Ordnung beträgt m2 / m1

Wo,

Die Anzahl der O / Ps für den Decoder niedrigerer Ordnung beträgt 'm1'.

Die Anzahl der O / Ps für Decoder höherer Ordnung beträgt 'm2'.

Wenn beispielsweise m1 = 4 & m2 = 8 ist, ersetzen Sie diese Werte in der obigen Gleichung. Wir können die erforderliche Nr. Erhalten. Die Anzahl der Decoder beträgt 2. Um einen einzelnen 3 bis 8 Decoder zu implementieren, benötigen wir zwei Decoder mit 2 bis 4 Zeilen. Hier wird das Blockdiagramm unten mit zwei 2 bis 4 Decodern gezeigt.

3 bis 8 Decoder mit 2 bis 4 Zeilen

Die parallelen Eingänge wie A2, A1 und A0 werden an 3-Zeilen-8-Zeilen-Decoder übergeben. Hier wird das Kompliment von A3 gegeben, damit der Pin des Decoders die Ausgänge wie Y7 bis Y0 erhalten kann. Diese Ausgänge sind niedrigere 8 Minuten. In dem obigen Decoder ist der A3-Eingang angeschlossen, damit der Pin die Ausgänge von Y15 - Y8 erhalten kann. Diese Ausgänge sind also die höheren 8 Minuten.

3-Zeilen- bis 8-Zeilen-Decoder mit Logikgattern

In einem 3 bis 8-Zeilen-Decoder enthält er drei Eingänge und acht Ausgänge. Hier werden die Eingänge durch A, B & C dargestellt, während die Ausgänge durch D0, D1, D2… D7 dargestellt werden.

Die Auswahl von 8 Ausgängen kann basierend auf den drei Eingängen erfolgen. Die Wahrheitstabelle dieses 3-Zeilen- bis 8-Zeilen-Decoders ist unten dargestellt. Aus der folgenden Wahrheitstabelle können wir ersehen, dass einfach einer von 8 Ausgängen von DO - D7 abhängig von 3 Auswahleingängen ausgewählt werden kann.

| ZU | B. | C. | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Aus der obigen Wahrheitstabelle von 3 Zeilen bis 8 Zeilen Decodierer kann der logische Ausdruck definiert werden als

D0 = A’B’C ’

D1 = A’B’C

D2 = A’BC ’

D3 = A’BC

D4 = AB’C ’

D5 = AB'C

D6 = ABC ’

D7 = ABC

Aus den obigen Booleschen Ausdrücken kann die Implementierung einer 3 bis 8-Decoderschaltung mit Hilfe von drei NOT-Gattern und 8-Drei-Eingangs-UND-Gattern erfolgen.

In der obigen Schaltung können die drei Eingänge in 8 Ausgänge decodiert werden, wobei jeder Ausgang eine der Zwischenzeiten der drei Eingangsvariablen darstellt.

Die 3 Wechselrichter in der obigen Logikschaltung stellen das Komplement der Eingänge bereit und jedes der UND-Gatter erzeugt eine der Zwischenzeiten.

Diese Art von Decoder wird hauptsächlich zum Decodieren eines 3-Bit-Codes verwendet und erzeugt acht Ausgänge, was 8 verschiedenen Kombinationen für den Eingangscode entspricht.

Dieser Decoder ist auch als Binär-Oktal-Decoder bekannt, da die Eingänge dieses Decoders Drei-Bit-Binärzahlen darstellen, während die Ausgänge die 8 Ziffern innerhalb des Oktalzahlensystems darstellen.

Blockdiagramm für 3-Zeilen- bis 8-Zeilen-Decoder

Diese Decoderschaltung bietet 8 Logikausgänge für 3 Eingänge und einen Freigabepin. Die Schaltung ist mit UND- und NAND-Logikgattern ausgelegt. Es benötigt 3 Binäreingänge und aktiviert einen der acht Ausgänge. 3 bis 8 Leitungsdecoderschaltung wird auch als Binär-zu-Oktal-Decoder bezeichnet.

Blockdiagramm für 3 bis 8 Zeilendecoder

Die Decoderschaltung funktioniert nur, wenn der Enable-Pin (E) hoch ist. S0, S1 und S2 sind drei verschiedene Eingänge und D0, D1, D2, D3. D4. D5. D6. D7 sind die acht Ausgänge. Das Logikdiagramm des 3- bis 8-Zeilen-Decoders wird unten gezeigt.

3 bis 8 Decoderschaltung

3 bis 8 Zeilendecoder und Wahrheitstabelle

Die folgende Tabelle gibt die Wahrheitstabelle des 3 bis 8-Zeilen-Decoders an.

| S0 | S1 | S2 | IS | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| x | x | x | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Wenn der Enable-Pin (E) niedrig ist, sind alle Ausgangspins niedrig.

1 bis 8 Demultiplexer

ZU Demultiplexer mit 1 bis 8 Zeilen hat einen Eingang, drei ausgewählte Eingangsleitungen und acht Ausgangsleitungen. Je nach ausgewähltem Eingang werden die Eingangsdaten auf 8 Ausgangsleitungen verteilt. Din sind die Eingangsdaten, S0, S1 und S2 sind Auswahleingänge und Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7 sind die Ausgänge.

1 bis 8 DEMUX

Das Schaltbild der 1 bis 8-Demux-Schaltung ist unten gezeigt.

1 bis 8 Demux-Schaltung

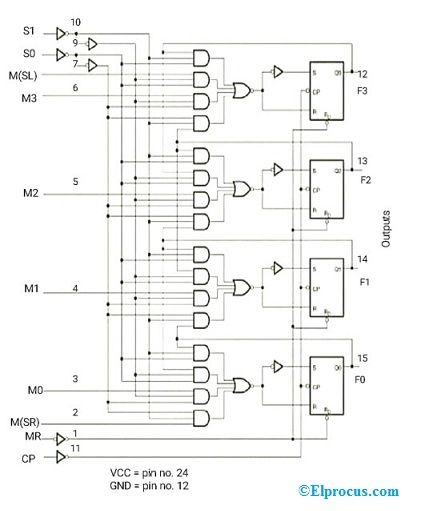

3 bis 8 Decoder / Demultiplexer

3 bis 8-Zeilen-Decoder-IC 74HC238 wird als Decoder / Demultiplexer verwendet. Der Demultiplexer mit 3 bis 8 Leitungsdecodern ist eine kombinatorische Schaltung, die sowohl als Decoder als auch als Demultiplexer verwendet werden kann. Der IC 74HC238 decodiert drei binäre Adresseneingänge (A0, A1, A2) in acht Ausgänge (Y0 bis Y7). Das Gerät verfügt außerdem über drei Enable-Pins. Die gleiche Kombination wird als Demultiplexer verwendet.

Pin-Konfiguration

Das Folgende ist die Pin-Konfiguration für den 3- bis 8-Zeilen-Decoder oder Demultiplexer IC74HC238. Es ist ein 16-poliger DIP.

Schaltkreis

Die logische Schaltung erklärt die Funktionsweise des IC 74HC238.

Merkmale des 74HC238 IC

- Demultiplexing-Fähigkeit

- Mehrere Eingänge ermöglichen eine einfache Erweiterung

- Ideal für die Decodierung von Speicherchips

- Aktive HIGH-Ausschlüsse, die sich gegenseitig ausschließen

- Option für mehrere Pakete

Anwendung des Decoders

- Das Decoder wurden bei der Analog-Digital-Wandlung in analogen Decodern verwendet.

- Wird in elektronischen Schaltkreisen verwendet, um Anweisungen in CPU-Steuersignale umzuwandeln.

- Sie verwendeten hauptsächlich in logische Schaltungen , Datentransfer.

Anwendungen von Demultiplexer

- Wird verwendet, um eine einzelne Quelle mit mehreren Zielen zu verbinden.

- Der Demux wird in Kommunikationssystemen verwendet, um mehrere Datensignale in eine einzige Übertragungsleitung zu übertragen.

- Wird in arithmetischen Logikeinheiten verwendet

- Wird in seriellen zu parallelen Wandlern in der Datenkommunikation verwendet.

Daher ist dies die grundlegende Information über 3 bis 8 Leitungsdecoder und Demultiplexer. Ich hoffe, Sie haben einige grundlegende Konzepte zu diesem Thema erhalten, indem Sie die digitalen Logikschaltungen und Wahrheitstabellen und ihre Anwendungen beobachtet haben. Darüber hinaus bestehen Zweifel an diesem Artikel oder dem Neueste Elektronikprojekte , Sie können Ihre Ansichten zu diesem Thema im Kommentarbereich unten schreiben.