Der MicroBlaze-Prozessor wurde 2002 entwickelt, um mehrere komplizierte Funktionen zu integrieren, um sowohl neuen als auch wachsenden Marktanforderungen gerecht zu werden. Daher ist der MicroBlaze-Prozessor ein wesentliches Element im Low-End-Portfolio von Xilinx, um eine schnellere Systementwicklung zu ermöglichen, die Artix®-7 enthält FPGAs , Spartan®-6, Zynq®-7000 AP SoCs. Dieser Prozessor ist extrem konfigurierbar, sodass er als eingebetteter Prozessor oder Mikrocontroller in FPGAs und auch als Co-Prozessor in den Zynq-7000-AP-SoCs auf Basis von ARM Cortex-A9 verwendet werden kann. Dieser Artikel enthält kurze Informationen zu MicroBlaze-Prozessor – Architektur und Arbeiten mit Anwendungen.

Was ist ein Microblaze-Prozessor?

Der Soft-Mikroprozessor, der hauptsächlich für FPGAs von Xilinx entwickelt wurde, ist als MicroBlaze-Prozessor bekannt. Dieser Prozessor wird einfach innerhalb der universellen Speicher- und Logikstruktur der FPGAs von Xilinx implementiert. Dieser Prozessor ähnelt der auf RISC basierenden DLX-Architektur und verfügt über ein flexibles Verbindungssystem, sodass er verschiedene eingebettete Anwendungen unterstützt. Der Haupt-E/A-Bus und die AXI-Verbindung des MicroBlaze ist ein speicherabgebildeter Transaktionsbus mit einer Master-Slave-Einrichtung.

MicroBlaze verwendet einen dedizierten LMB-Bus für den Zugriff auf den lokalen Speicher und bietet schnellen On-Chip-Speicher. Viele Teile dieses Prozessors können vom Benutzer konfiguriert werden, wie z. B. die Größe des Caches, die Tiefe der Pipeline-Speicherverwaltungseinheit, eingebettete Peripheriegeräte und Busschnittstellen.

Microblaze-Funktionen

Das Funktionen von Microblaz Dazu gehören die folgenden. Es verfügt über 32 Allzweckregister.

- Es verfügt über 32-Bit-Befehlswörter, einschließlich 2 Adressierungsmodi und 3 Operanden.

- Der Adressbus ist 32-Bit.

- Es hat eine 3-stufige Pipeline oder eine 5-stufige Pipeline.

- Eine ALU-Blockeinheit mit Schalthebel.

- Die Harvard-Architektur umfasst einen 32-Bit-Daten- und Adressbus.

- Datenschnittstelle & LMB oder lokaler Speicherbusbefehl.

- AX14- und AX14-Stream-Schnittstellen.

- Gleitkommaeinheit und Speicherverwaltungseinheit.

- Es unterstützt Lockstep.

- Debug & Trace-Schnittstelle.

Microbaze-Architektur

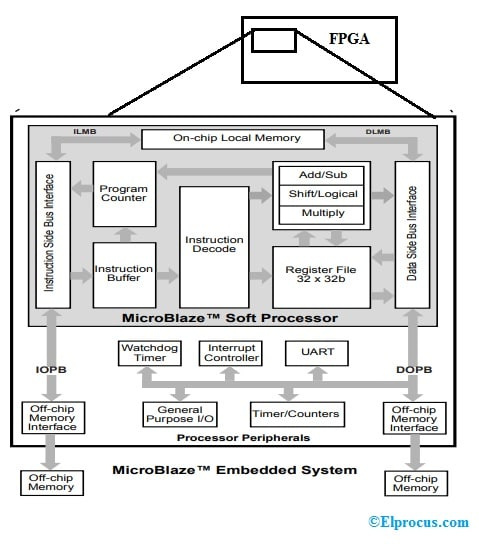

Das Blockdiagramm des MicroBlaze-Prozessors ist unten dargestellt. Dieser MicroBlaze-Prozessor ist extrem anpassbar und unterstützt über 70 Designoptionen. Diese Architektur zeigt permanente Hardwarefunktionen sowie konfigurierbare Optionen wie den Befehls- oder Datencache, die Speicherverwaltungseinheit, die Gleitkommaeinheit usw.

Ein Eingebettetes System die um einen MicroBlaze-Prozessor herum aufgebaut sind, umfassen hauptsächlich MicroBlaze Soft Processor Core, On-Chip Local Memory, Standard Bus Interconnects und OPB Peripherals (On-Chip Peripheral Bus). Ein MicroBlaze-Prozessorsystem reicht hauptsächlich von einem Prozessorkern durch einen lokalen Speicher bis zu einem großen System, das mehrere MicroBlaze umfasst Prozessoren , externer Speicher und viele OPB-Peripheriegeräte.

Weicher Prozessorkern

Der Softprozessorkern von MicroBlaze ist das Herzstück des MicroBlaze-Embedded-Systems. Dies ist ein sehr schneller und effizienter 32-Bit-RISC-Prozessor mit den folgenden Merkmalen.

- Der Befehlssatz ist orthogonal.

- Separate Daten- und Befehlsbusse.

- 32-Bit-Universalregister.

- Es verfügt über einen optionalen vollständigen 32-Bit-Barrel-Shifter.

- Integrierte Schnittstellen zu schnellem OCM oder On-Chip-Speicher und IBMs Industriestandard OPB (On-Chip Peripheral Bus).

Implementierungen innerhalb von Virtex-II und späteren Geräten unterstützen eine Vielzahl von Hardware.

Lokaler On-Chip-Speicher

Der synchrone Speicher ist ein lokaler Speicher, der hauptsächlich verwendet wird, um On-Chip-Block-RAM zu ermöglichen.

Standard-Busverbindungen

Die Busschnittstellen auf der Befehls- und Datenseite umfassen eine Schnittstelle zum lokalen Speicher, die LMB (Local Memory Bus) genannt wird, und eine Schnittstelle zum On-Chip Peripheral Bus von IBM. So können wir Systeme entwerfen, die sich strikt an die Harvard-Architektur halten, andernfalls können wir, um Ressourcen gemeinsam zu nutzen, einen einzelnen OPB innerhalb einer Kombination durch einen Bus-Arbiter verwenden.

Der lokale Speicherbus bietet einen gesicherten Single-Cycle-Eingang für On-Chip-Block-RAM. Dies ist ein sehr effizientes, einfaches Single-Master-Busprotokoll, das sich perfekt für die Anbindung schneller lokaler Speicher eignet. Der OPB oder On-Chip Peripheral Bus ist ein 32 Bit breiter Multi-Master-Bus, der sich perfekt dafür eignet, Peripheriegeräte und externen Speicher mit dem Kern des MicroBlaze-Prozessors zu vereinen.

On-Chip-Peripheriebus-Peripheriegeräte

Das MicroBlaze-Hardwaresystem wird durch OPB-Peripheriegeräte vervollständigt, um verschiedene Funktionen wie Watchdog-Timer oder Zeitbasis, Allzweck-Timer oder -Zähler, IC (Interrupt Controller), verschiedene Controller wie SRAM, Flash-Speicher, ZBT-Speicher, BRAM, DDR, SDRAM, UART Lite bereitzustellen , SPI, I2C, Mehrzweck-E/A, UART 16450/550 und Ethernet 10/100 MAC. Darüber hinaus können wir Peripheriegeräte hauptsächlich für benutzerdefinierte Funktionen hinzufügen und definieren, ansonsten eine Schnittstelle zu einem Design, das im FPGA vorhanden ist.

Microblaze-Anweisungssatz

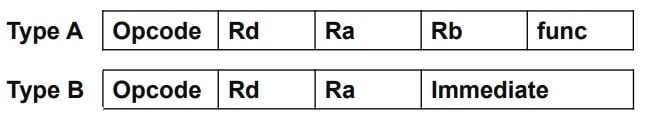

Microblaze-Befehlssätze sind Arithmetik, Logik, Verzweigung, Laden/Speichern und andere. Die Größe aller Anweisungen ist festgelegt. Als Operanden können maximal 3 Register angegeben werden. Microblaze enthält zwei Anweisungsformate Typ A und Typ B, die unten gezeigt werden.

Das Befehlsformat Typ A wird hauptsächlich für Register-Register-Befehle verwendet. Es enthält also den Opcode, ein einziges Ziel und zwei Quellregister. Das Befehlsformat Typ B wird hauptsächlich für Register-Immediate-Befehle verwendet, die Opcode-, Einzelziel- und Einzelquellenregister sowie eine 16-Bit-Direktwertquelle enthalten.

In den beiden obigen Befehlsformaten ist der Opcode ein Operationscode, Rd ist ein Zielregister, das mit 5 Bit codiert ist, Ra und Rb sind Quellregister, wobei jedes mit 5 Bit codiert ist, und Immediate ist ein 16-Bit-Wert.

Arithmetische Anweisungen

Die Arithmetikbefehle vom Typ A und Typ B sind unten angegeben.

Tippe A

|

Rd, Ra, Rb HINZUFÜGEN hinzufügen |

Rd = Ra+Rb, Carry-Flag betroffen |

|

HINZUFÜGEN K Rd, Ra, Rb Hinzufügen und weitertragen |

Rd = Ra+Rb, Carry-Flag nicht betroffen |

| RSUB Rd, Ra, Rb Rückwärts subtrahieren |

Rd = R-Rb, Carry-Flag nicht betroffen |

Typ B

|

HINZUFÜGEN I Rd, Ra, Imm sofort hinzufügen |

Rd = Ra+signExtend32 (Imm) |

|

HINZUFÜGEN IK Rd, Ra, Imm sofort hinzufügen und weitertragen |

Rd = Ra+ signExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm umgekehrt subtrahieren mit unmittelbar |

Rd = Ra+ signExtend32 (Imm)-Ra |

| SRA Rd, Ra arithmetische Verschiebung nach rechts |

Rd = (Ra>>1) |

Logikanweisungen

Die Logikbefehle vom Typ A und Typ B sind unten angegeben.

Tippe A

|

ODER Rd, Ra, Rb Logisch bzw |

Rd = Ra| Rb |

|

UND Rd, Ra, Rb Logische Ergänzung |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb Logisches xor |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Logisch und nicht |

Rd = Ra & (Rb) |

Typ B

|

ORI Rd, Ra, Imm logisches ODER mit unmittelbarem |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm logisches UND mit unmittelbar |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm logisches XOR mit unmittelbarem |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Logisch UND NICHT mit Sofort |

Rd = Ra & (signExtend32 (Imm)) |

Verzweigungsanweisungen – Unbedingt

Ändern Sie das Programmzählerregister

| BRID Imm Filiale sofort mit sofortiger Verzögerung |

PC = PC+ signExtend32 (Imm) Verzögerungsschlitzausführung zulassen |

| BRLID Rd, Imm sofort verzweigen und verbinden mit sofortiger Verzögerung (Funktionsaufruf) |

Rd = PC PC = PC+& signExtend32 (Imm) Verzögerungsschlitzausführung zulassen |

| RTSD Ra, Imm Rückkehr vom Unterprogramm |

PC = Ra + signExtend32 (Imm) Verzögerungsschlitzausführung zulassen |

| RTID Ra, Imm Rückkehr vom Interrupt |

PC = Ra + signExtend32 (Imm) Verzögerungsschlitzausführung zulassen Interruptfreigabe in MSR setzen |

Verzweigungsbefehle – unbedingt1

Ändern Sie das Programmzählerregister, wenn eine Bedingung erfüllt ist

| BEQI Ra, Imm Verzweigung falls gleich |

PC = PC+ signExtend32 (Imm) Wenn Ra = = 0 |

| BREI Ra, Imm Verzweigung, wenn nicht gleich |

Rd = PC PC = PC+& signExtend32 (Imm) Wenn Ra! = 0 |

Verzweigungsbefehle – unbedingt2

Ändern Sie das Programmzählerregister, wenn eine Bedingung erfüllt ist

| BLTI Ra, Imm Verzweigung, wenn kleiner als |

PC = PC+ signExtend32 (Imm) Wenn Ra < 0 |

| BLEI Ra, Imm Verzweigung, wenn kleiner gleich als |

Rd = PC PC = PC+& signExtend32 (Imm) Wenn Ra!< = 0 |

| BGTI Ra, Imm Verzweigung, wenn größer als |

PC = PC+ signExtend32 (Imm) Wenn Ra! > 0 |

| BGEI Ra, Imm Verzweigung, wenn größer gleich als |

PC = PC+signExtend32 (Imm) Wenn Ra!>= 0 |

Anweisungen zum Laden/Speichern – Typ A

| LW Rd, Ra, Rb Wort laden |

Adresse = Ra+Rb Rd = *Adresse |

| SW Rd, Ra, Rb Wort speichern |

Adresse – Ra+Rb *Adresse = Rd |

Typ B

| LWI Rd, Ra, Imn Wort sofort laden |

Adresse = Ra + signExtend32 (Imm) Rd = *Adresse |

| SW Rd, Ra, Imm Wort sofort speichern |

Adresse = Ra + signExtend32 (Imm) *Adresse = Rd |

Andere Anweisungen

| IM, Imm sofort |

Erweitern Sie den Imm eines vorangehenden Typ-B-Befehls auf 32 Bit. |

| MFS Rd, Sa Auszug aus dem Sonderregister |

Rd = Sa Sa- Spezialregister, Quellenoperand

|

| MTS SD, Ra Wechsel in das Sonderregister |

SD = Ra Sd – Spezialregister, Zieloperand |

Register

Die Architektur des MicroBlaze-Prozessors ist vollständig orthogonal und umfasst 32-Bit-Allzweckregister und 32-Bit-Spezialregister wie Programmzähler und Maschinenstatusregister.

Pipeline-Architektur

MicroBlaze verwendet eine dreistufige Pipeline-Architektur, einschließlich Abruf-, Dekodierungs- und Abschlussphasen. Innerhalb der Hardware werden automatisch die Datenweiterleitung, Branches & Pipeline-Stall ermittelt.

Architektur laden oder speichern

MicroBlaze unterstützt Speicher in drei Datengrößen: 8 Bit (Byte), 16 Bit (Halbwort) und 32 Bit (Wort). Speicherzugriffe sind also immer an der Datengröße ausgerichtet. Dies ist ein Big-Endian-Prozessor, der die Adresse der Big-Endian-Adresse sowie Kennzeichnungskonventionen verwendet, sobald auf den Speicher zugegriffen wird.

Unterbricht

Sobald eine Unterbrechung stattfindet, beendet dieser Prozessor die aktuelle Ausführung, um die Unterbrechungsanforderung durch Verzweigung zur Unterbrechungsvektoradresse zu verwalten und die auszuführende Befehlsadresse zu speichern. Dieser Prozessor stoppt zukünftige Interrupts, indem er das IE-Flag (Interrupt Enable) im MSR (Machine Status Register) löscht.

Wie funktioniert Microblaze?

Der MicroBlaze-Prozessor unterstützt 32-Bit-Busbreite und dieser Prozessorkern ist eine RISC-basierte Engine, die eine Registerdatei basierend auf 32-Bit-LUT-RAM durch separate Anweisungen für Speicher- und Datenzugriff enthält.

Dieser Prozessor unterstützt einfach sowohl On-Chip-BlockRAM als auch externen Speicher. Ähnlich dem IBM PowerPC; alle Peripheriegeräte verwenden daher den ähnlichen CoreConnect OPB-Bus; Die Peripherie des Prozessors ist gut auf PowerPC auf Virtex-II Pro abgestimmt.

Der MicroBlaze-Prozessor bietet vollständige Flexibilität bei der Auswahl der Kombination aus Speicher-, Peripherie- und Schnittstellenfunktionen, die Ihnen genau das System bieten, das Sie auf einem einzigen FPGA zu geringeren Kosten benötigen.

Unterschied S/W Microblaze Vs Risc-V

Das Unterschied zwischen MicroBlaze und RISC v füge folgendes hinzu.

|

Mikrobrand |

Risiko-V |

| Es ist ein weicher Mikroprozessorkern, der hauptsächlich für Xilinx FPGA entwickelt wurde.

|

RISC-V ist eine Befehlssatzarchitektur, die auf RISC-Prinzipien basiert.

|

| Es verwendet die Harvard RISC-Architektur. | Es verwendet eine Befehlssatzarchitektur. |

| Die Lizenz ist proprietär (Xilinx) | Seine Lizenz ist Open Source. |

| Die Tiefe der Pipeline beträgt 3 oder 5. | Die Tiefe der Pipeline beträgt 5. |

| Seine Leistung beträgt 280 DMIPs. | Seine Leistung beträgt 250 DMIPs. |

| Seine Geschwindigkeit beträgt 235 MHz. | Seine Geschwindigkeit beträgt 250 MHz. |

| Es hat 1027 LUTs. | Es hat 4125 LUTs. |

| Die Implementierung der verwendeten Technologie ist Xilinx FPGA. | Die Implementierung der verwendeten Technologie ist FPGA/ASIC. |

Microblaze-Vorteile

Das Vorteile von MicroBlaze füge folgendes hinzu.

- Es ist wirtschaftlich.

- Es ist hochgradig konfigurierbar.

- Seine Leistung ist im Vergleich zu ARM hoch.

- Es wird von einem eingebetteten Entwicklungskit unterstützt.

- Es ist eine weiche Mikroprozessor Ader.

- Um Ihnen bei der schnellen Zusammenstellung Ihrer Anwendung zu helfen, enthält dieser Prozessor drei feste Konfigurationen, die sich auf bekannte Prozessorklassen Mikrocontroller, Echtzeit- und Anwendungsprozessor beziehen.

Microblaze-Anwendungen

Das Anwendungen von MicroBlaze füge folgendes hinzu.

- Dieser Prozessor erfüllt viele verschiedene Anwendungsanforderungen wie Industrie, Automobil, Medizin und Verbraucher usw.

- Die Anwendungen von MicroBlaze reichen von einfachen Zustandsmaschinen auf Softwarebasis bis hin zu komplexen Controllern, die in eingebetteten Anwendungen oder internetbasierten Geräten verwendet werden.

- Es ist für eingebettete Anwendungen wie Industriesteuerung, Büroautomatisierung und Automotive optimiert.

- Der MicroBlaze ist in der Lage, mit einer großen Anzahl von Peripheriegeräten zu kommunizieren, um in mittelgroße Anwendungen zu passen.

- Die weiche Natur dieses Prozessors macht ihn für verschiedene Anwendungen anpassbar, bei denen Designer Features gegen Größe austauschen können, um Preis- und Leistungsziele für medizinische, Automobil-, Industrie- und Sicherheitsanwendungen zu erreichen.

Es geht also um alles eine Übersicht über die Microblaze Prozessor. Dies ist ein voll ausgestatteter, programmierbarer 32-Bit-RISC-Soft-Prozessorkern. Dieser Prozessor erfüllt unterschiedliche Anforderungen in verschiedenen Bereichen wie Verbraucher-, Medizin-, Industrie-, Automobil- und Kommunikationsinfrastrukturmärkten. Es ist extrem konfigurierbar und wird daher als eingebetteter Prozessor oder Mikrocontroller in FPGAs verwendet, ansonsten wie ein Co-Prozessor für den ARM. Hier ist eine Frage an Sie, was ist FPGA?