RISC V ist eine von der University of California, Berkeley, entwickelte Befehlssatzarchitektur. Das Konzept von RISC wurde durch die Tatsache motiviert, dass die meisten Prozessorbefehle von den meisten Computerprogrammen nicht verwendet werden. Daher wurde in den Designs von unnötige Dekodierungslogik verwendet Prozessoren , verbrauchen mehr Energie sowie Fläche. Um den Befehlssatz zu verkürzen und mehr in Registerressourcen zu investieren, die RISC V-Prozessor wurde implementiert.

Diese Technologie wurde von vielen Technologiegiganten und Start-ups bemerkt, da sie vollständig Open Source und kostenlos ist. Die meisten Prozessortypen sind mit einer Lizenzvereinbarung erhältlich, jedoch mit diesem Prozessortyp; Jeder kann seine neuen Prozessordesigns erstellen. Daher behandelt dieser Artikel einen Überblick über einen RISC V-Prozessor – die Funktionsweise und seine Anwendungen.

Was ist der RISC V-Prozessor?

Beim RISC V-Prozessor steht der Begriff RISC für „Reduced Instruction Set Computer“, der wenige Computerbefehle ausführt, während „V“ für die 5. Generation steht. Es ist eine Open-Source-Hardware-ISA (Instruction Set Architecture), die auf dem etablierten Prinzip von basiert RISIKO .

Im Vergleich zu anderen ISA-Designs ist diese ISA mit einer Open-Source-Lizenz erhältlich. Daher haben eine Reihe von Herstellern RISC-V-Hardware mit Open-Source-Betriebssystemen angekündigt und auch bereitgestellt.

Dies ist eine neue Architektur und ist in offenen, uneingeschränkten und kostenlosen Lizenzen verfügbar. Dieser Prozessor wird umfassend von Chip- und Geräteherstellern unterstützt. Daher ist es hauptsächlich so konzipiert, dass es frei erweiterbar und anpassbar ist, um es in vielen Anwendungen zu verwenden.

RISC V-Geschichte

Der RISC wurde um 1980 von Prof. David Patterson an der University of California, Berkeley, erfunden. Prof. David und Prof. John Hennessy haben ihre Bemühungen in zwei Büchern eingereicht, nämlich „Computer Organization and Design“ und „Computer Architecture at Stanford University. Also erhielten sie die ACM A.M. Turing-Preis im Jahr 2017.

Von 1980 bis 2010 wurde die RISC-Entwicklungsforschung der fünften Generation gestartet und schließlich als RISC-V identifiziert, was als Risiko fünf bezeichnet wird.

RISC V Architektur & Arbeiten

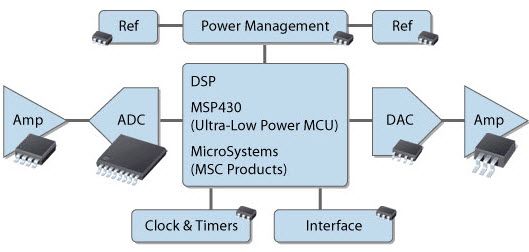

Die RV12 RISC V-Architektur ist unten dargestellt. Der RV12 ist mit einer Single-Core-RV32I- und RV64I-kompatiblen RISC-CPU, die in eingebetteten Bereichen verwendet wird, hochgradig konfigurierbar. Der RV12 stammt ebenfalls aus einer 32- oder 64-Bit-CPU-Familie, abhängig vom Industriestandard-RISC-V-Befehlssatz.

Der RV12 führt einfach eine Harvard-Architektur für den gleichzeitigen Zugriff auf Befehle und Datenspeicher aus. Es enthält auch eine 6-stufige Pipeline, die hilft, Überlappungen zwischen der Ausführung sowie Speicherzugriffe zu optimieren, um die Effizienz zu verbessern. Diese Architektur umfasst hauptsächlich Verzweigungsvorhersage, Datencache, Debugeinheit, Befehlscache und optionale Multiplikator- oder Teilereinheiten.

Zu den Hauptmerkmalen des RV12 RISC V gehören die folgenden.

- Es ist ein Befehlssatz nach Industriestandard.

- Parametriert mit 32 oder 64bit Daten.

- Es hat präzise und schnelle Interrupts.

- Benutzerdefinierte Anweisungen ermöglichen das Hinzufügen von proprietären Hardwarebeschleunigern.

- Ausführung Einzelzyklus.

- Sechsstufige Rohrleitung mit Optimierung gefaltet.

- Unterstützung mit Speicherschutz.

- Optionale oder parametrisierte Caches.

- Extrem parametrisiert.

- Benutzer können 32/64-Bit-Daten und Branch Prediction Unit auswählen.

- Benutzer können Anweisungs-/Daten-Caches auswählen.

- Vom Benutzer wählbare Struktur, Größe und Architektur des Caches.

- Hardware-Teiler oder Multiplikator-Unterstützung durch benutzerdefinierte Latenz.

- Die Busarchitektur ist flexibel und unterstützt Wishbone & AHB.

- Dieses Design optimiert die Leistung und Größe.

- Das Design ist vollständig parametrisiert, was Leistungs- oder Leistungskompromisse bietet.

- Gated CLK-Design zur Leistungsreduzierung.

- Softwareunterstützung nach Industriestandard.

- Architektursimulator.

- Eclipse IDE wird für Linux/Windows verwendet.

Die RISC V-Ausführungspipeline

Es umfasst fünf Stufen wie IF (Befehlsabruf), ID (Befehlsdecodierung), EX (Ausführen), MEM (Speicherzugriff) und WB (Registerrückschreiben).

Anweisung abrufen

In der Anweisungsabruf- oder IF-Stufe wird eine einzelne Anweisung aus dem Programmzähler (PC) und dem Anweisungsspeicher gelesen, der auf die nächste Anweisung aktualisiert wird.

Anweisung Pre-Decode

Sobald die RVC-Unterstützung erlaubt ist, decodiert die Anweisungs-Vordecodierungsstufe eine 16-Bit-komprimierte Anweisung in eine native 32-Bit-Anweisung.

Anweisung decodieren

In der Stufe der Befehlsdecodierung (ID) wird die Registerdatei zugelassen und die Umgehungssteuerungen werden entschieden.

Ausführen

In der Ausführungsphase wird das Ergebnis für einen ALU-, DIV-, MUL-Befehl, der für einen Store- oder Load-Befehl zulässige Speicher berechnet, und Verzweigungen und Sprünge werden mit ihren erwarteten Ergebnissen verglichen.

Erinnerung

In dieser Speicherstufe wird über die Pipeline auf den Speicher zugegriffen. Die Einbeziehung dieser Phase stellt die hohe Leistung der Pipeline sicher.

Schreib zurück

In dieser Stufe wird das Ergebnis der Ausführungsstufe in die Registerdatei geschrieben.

Branchenprädiktor

Dieser Prozessor enthält eine Verzweigungsvorhersageeinheit oder BPU, die verwendet wird, um frühere Daten zu speichern, um den RISC-V-Prozessor bei der Entscheidung zu führen, ob eine bestimmte Verzweigung genommen wird oder nicht. Diese Prädiktordaten werden einfach aktualisiert, sobald die Verzweigung ausgeführt wird.

Diese Einheit enthält verschiedene Parameter, die ihr Verhalten bestimmen. Beispielsweise wird HAS_BPU verwendet, um zu bestimmen, ob eine Verzweigung das Vorhandensein einer Einheit vorhersagt, BPU_GLOBAL_BITS bestimmt, wie viele vergangene Bits verwendet werden sollten, und BPU_LOCAL_BITS bestimmt, wie viele der LSB des Programmzählers verwendet werden sollten. Die Kombination von BPU_LOCAL_BITS & BPU_GLOBAL_BITS erzeugt einen Vektor, der hauptsächlich verwendet wird, um die Branch-Prediction-Table zu adressieren.

Datencache

Dies wird hauptsächlich verwendet, um den Zugriff auf den Datenspeicher zu beschleunigen, indem neu zugegriffene Speicherorte gepuffert werden. Dies ist in der Lage, Halbwort-, Byte- und Wortzugriffe zu verarbeiten, wenn XLEN = 32, wenn sie sich auf ihren eigenen Grenzen befinden. Es ist auch in der Lage, Halbwort-, Byte-, Wort- und Doppelwortzugriffe zu handhaben, wenn XLEN = 64, wenn sie sich auf ihren eigenen Grenzen befinden.

Während eines Cache-Miss kann ein ganzer Block in den Speicher zurückgeschrieben werden, sodass bei Bedarf ein neuer Block in den Cache geladen werden kann. Der Datencache wird deaktiviert, indem DCACHE_SIZE auf Null gesetzt wird. Danach wird direkt über die auf Speicherplätze zugegriffen Datenschnittstelle .

Anweisungs-Cache

Dies wird hauptsächlich verwendet, um das Abrufen von Befehlen zu beschleunigen, indem neu abgerufene Befehle gepuffert werden. Dieser Cache wird verwendet, um ein Paket für jeden Zyklus auf einer beliebigen 16-Bit-Grenze, aber nicht über eine Blockgrenze hinweg, abzurufen. Während eines Cache-Fehltreffers kann ein ganzer Block aus dem Befehlsspeicher geladen werden. Die Konfiguration dieses Caches kann basierend auf den Bedürfnissen des Benutzers erfolgen. Die Größe des Caches, der Ersetzungsalgorithmus und die Blocklänge sind konfigurierbar.

Der Befehlszyklus wird deaktiviert, indem ICACHE_SIZE auf Null gesetzt wird. Danach werden Pakete direkt aus dem Speicher durch die geholt Anweisungsschnittstelle.

Debug-Einheit

Die Debug-Einheit ermöglicht es der Debug-Umgebung, die CPU anzuhalten und zu untersuchen. Die Hauptmerkmale davon sind Branch Tracing, Single Step Tracing bis zu 8 Hardware Breakpoints.

Datei registrieren

Dies ist mit 32 Registerstellen von X0 bis X31 ausgelegt, wobei das X9-Register immer Null ist. Die Registerdatei enthält 1 Schreibport und 2 Leseports.

Konfigurierbare Schnittstelle

Dies ist eine externe Schnittstelle, wobei dieser Prozessor verschiedene externe Busschnittstellen unterstützt.

Wie funktioniert RISC V?

RISC-V ist eine Befehlssatzarchitektur, die auf den RISC-Prinzipien (Reduced Instruction Set Computer) basiert. Dieser Prozessor ist sehr einzigartig und auch revolutionär, da es sich um eine kostenlose, gemeinsame und Open-Source-ISA handelt, bei der Hardware entwickelt, die Software portiert und Prozessoren entwickelt werden können, um sie zu unterstützen.

Unterschied S/W RISC V Vs MIPS

Der Unterschied zwischen RISC V und MIPS umfasst Folgendes.

|

RISC V |

MIPS |

| Der Begriff RISC V steht für Computer mit reduziertem Befehlssatz, wobei „V“ für die fünfte Generation steht. | Der Begriff „MIPS“ steht für „Millionen Anweisungen pro Sekunde“. |

| RISC-V ermöglicht es den Herstellern kleinerer Geräte einfach, Hardware zu entwerfen, ohne dafür zu bezahlen. | MIPS ermöglicht es dem Hersteller, die Geschwindigkeit des Prozessors zu messen, indem er bezahlt, da es nicht kostenlos ist. |

| MIPS ist praktisch tot. | RISC-V ist nicht effizient tot. |

| Dieser Prozessor liefert Verzweigungsbefehle zum Vergleichen zweier Register. | MIPS hängt von einem Vergleichsbefehl ab, der ein Register auf 1 oder 0 lokalisiert, je nachdem, ob der Kontrast wahr ist. |

| Das ISA-Codierungsschema ist in RISC V fest und variabel. | Das ISA-Codierungsschema ist in MIPS festgelegt |

| Die Befehlssatzgröße ist 16-Bit oder 32-Bit oder 64-Bit oder 128-Bit. | Die Befehlssatzgröße ist 32-Bit oder 64-Bit. |

| Es hat 32 Mehrzweck- und Gleitkommaregister | Es verfügt über 31 Allzweck- und Gleitkommaregister. |

| Es verfügt über 26 Gleitkommaoperationen mit einfacher und doppelter Genauigkeit. | Es verfügt über 15 Gleitkommaoperationen mit einfacher und doppelter Genauigkeit. |

Unterschied S/W RISC V Vs ARM

Der Unterschied zwischen RISC V Vs ARM umfasst Folgendes.

|

RISC V |

ARM |

| RISC-V ist Open Source und erfordert daher keine Lizenz. | ARM ist eine geschlossene Quelle, daher ist eine Lizenz erforderlich. |

| Es handelt sich um eine neue Prozessorplattform, daher gibt es nur sehr wenig Unterstützung für Software- und Programmierumgebungen. | ARM hat eine sehr große Online-Community, die Bibliotheken und Strukturen unterstützt, um die Zieldesigner auf verschiedenen Plattformen wie Mikroprozessoren, Mikrocontrollern und auch Servern zu unterstützen. |

| RISC V-basierte Chips verbrauchen 1 Watt Leistung. | ARM-basierte Chips verbrauchen weniger als 4 Watt Leistung. |

| Es verfügt über ein festes und variables ISA-Codierungssystem. | Es hat ein festes ISA-Codierungssystem. |

| Die Größe des RISC V-Befehlssatzes reicht von 16 Bit bis 128 Bit. | Seine Befehlsgröße reicht von 16 Bit bis 64 Bit. |

| Es enthält 32 Allzweck- und Gleitkommaregister. | Es enthält 31 Allzweck- und Gleitkommaregister. |

| Es verfügt über 26 Gleitkommaoperationen mit einfacher Genauigkeit. | Es verfügt über 33 Gleitkommaoperationen mit einfacher Genauigkeit. |

| Es verfügt über 26 Gleitkommaoperationen mit doppelter Genauigkeit. | Es verfügt über 29 Gleitkommaoperationen mit doppelter Genauigkeit. |

RISC V Verilog-Code

Der Befehlsspeicher-Verilog-Code für RISC ist unten gezeigt.

// Verilog-Code für RISC-Prozessor

// Verilog-Code für den Befehlsspeicher

Modul Instruction_Memory(

Eingabe[15:0] PC,

output[15:0]-Anweisung

);

reg [`col – 1:0] Speicher [`row_i – 1:0];

Draht [3: 0] rom_addr = pc [4: 1];

Initial

Start

$readmemb(./test/test.prog“, Speicher,0,14);

Ende

Anweisung zuweisen = Speicher [rom_addr];

Endmodul

Verilog-Code für den 16-Bit-RISC-V-Prozessor:

Modul Risc_16_bit(

Eingabe clk

);

Drahtsprung, bne, beq, mem_read, mem_write, alu_src, reg_dst, mem_to_reg, reg_write;

Draht[1:0] alu_op;

Draht [3:0] Opcode;

// Datenweg

Datenpfad_Einheit DU

(

.clk(clk),

.springen (springen),

.frog(Frosch),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// Steuergerät

Control_Unit-Steuerung

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.springen (springen),

.bne(bne),

.frog(Frosch),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

Endmodul

Befehlssätze

Die RISC V-Befehlssätze werden unten diskutiert.

Rechenoperationen

Die arithmetischen Operationen von RISC V sind unten aufgelistet.

| Mnemonik | Typ | Anweisung | Beschreibung |

| HINZUFÜGEN rd, rs1, rs2 |

R |

Hinzufügen | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

R |

Subtrahieren | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

ich |

Sofort hinzufügen | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

R |

Kleiner als einstellen | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

ich |

Weniger als sofort einstellen | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

R |

Setzen Sie weniger als unsigned | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

ich |

Legen Sie weniger als unmittelbar unsigniert fest | rdß rs1 -< imm12 |

| LUI rd, imm20 |

IN |

Obere sofort laden | rdß imm20<<12 |

| AUIP rd, imm20 |

IN |

Fügen Sie dem PC das obere Direkt hinzu | rdß PC+imm20<<12 |

Logische Operationen

Die logischen Operationen von RISC V sind unten aufgelistet.

| Mnemonik | Typ | Anweisung | Beschreibung |

| UND rd, rs1, rs2 |

R |

UND | rdß rs1 & rs2 |

| ODER rd, rs1, rs2 |

R |

ODER | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

FREI | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

ich |

UND sofort | rdß rs1 & imm2 |

| ORI rd, rs1, imm12 |

ich |

ODER Sofort | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

ich |

XOR sofort | rdß rs1 ^ rs2 |

| SLL-rd, rs1, rs2 |

R |

Linksverschiebung logisch | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

R |

Rechtsverschiebung logisch | rdß rs1 >> rs2 |

| RAS-rd, rs1, rs2 |

R |

Arithmetik nach rechts verschieben | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

ich |

Logisch unmittelbar nach links verschieben | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

ich |

Logisch sofort nach rechts verschieben | rdß rs1 >> shamt |

| SRAI-rd, rs1, shamt |

ich |

Arithmetik sofort nach rechts verschieben | rdß rs1 >> shamt |

Lade-/Speicheroperationen

Die RISC V-Lade-/Speicheroperationen sind unten aufgelistet.

| Mnemonik | Typ | Anweisung | Beschreibung |

| LD rd, imm12 (rs1) |

ich |

Doppelwort laden | rdß mem [rs1 +imm12] |

| LW rt, imm12 (rs1) |

ich |

Wort laden | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

ich |

Auf halbem Weg laden | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

ich |

Byte laden | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

ich |

Wort ohne Vorzeichen laden | rdß mem [rs1 +imm12] |

| LHU rt, imm12 (rs1) |

ich |

Halbwort ohne Vorzeichen laden | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

ich |

Byte ohne Vorzeichen laden | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

S |

Doppelwort speichern | rs2 zu mem [rs1 + imm12] |

| Software rs2, imm12 (rs1) |

S |

Wort speichern | rs2 (31:0) an mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

S |

Auf halbem Weg lagern | rs2 (15:0) an mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

S |

Byte speichern | rs2 (15:0) an mem [rs1 +imm12] |

| SRAI-rd, rs1, shamt |

ich |

Arithmetik sofort nach rechts verschieben | rs2 (7:0) an mem [rs1 +imm12] |

Verzweigungsoperationen

Die RISC V-Verzweigungsoperationen sind unten aufgelistet.

| Mnemonik | Typ | Anweisung | Beschreibung |

| BEQ rs1, rs2, imm12 |

SB |

Zweig gleich | Wenn rs1== rs2 PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

Zweig nicht gleich | Wenn rs1!= rs2 PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

Verzweigung größer oder gleich | Wenn rs1>= rs2 PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

Verzweigung größer oder gleich unsigned | Wenn rs1>= rs2 PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

Zweig weniger als | Wenn rs1 < rs2 PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

Weniger als unsigniert verzweigen | Wenn rs1 < rs2 PC ß PC+imm12 <<1 |

| JAL rd, imm20 |

UJ |

Springen und verlinken | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

ich |

Jump and Link registrieren | rdßPC+4 PCß rs1+imm12 |

Vorteile

Das Vorteile des RISC V-Prozessor füge folgendes hinzu.

- Durch die Verwendung von RISCV können wir Entwicklungszeit, Softwareentwicklung, Verifizierung usw. einsparen.

- Dieser Prozessor hat viele Vorteile wie Einfachheit, Offenheit, Modularität, sauberes Design und Erweiterbarkeit.

- Dies wird von mehreren Sprachcompilern wie dem GCC (GNU Compiler Collection), einem Compiler für freie Software, unterstützt Linux-Betriebssystem .

- Dies kann von Unternehmen frei verwendet werden, da keine Lizenzgebühren, keine Lizenzgebühren und keine Bedingungen verbunden sind.

- Der RISC-V-Prozessor enthält keine neuen oder innovativen Funktionen, da er einfach den etablierten Prinzipien von RISC folgt.

- Ähnlich wie bei mehreren anderen ISAs definiert diese Prozessorspezifikation einfach verschiedene Befehlssatzebenen. Dies enthält also 32- und 64-Bit-Varianten sowie Erweiterungen zur Unterstützung von Gleitkommaanweisungen.

- Diese sind kostenlos, einfach, modular, stabil usw.

Nachteile

Das Nachteile des RISC V Prozessors füge folgendes hinzu.

- Komplexe Anweisungen werden häufig von Compilern und Programmierern verwendet.

- Das o/p eines RISC kann sich basierend auf dem Code ändern, wenn nachfolgende Anweisungen innerhalb einer Schleife von der früheren Anweisung zur Ausführung abhängen.

- Diese Prozessoren müssen schnell eine Vielzahl von Befehlen speichern, was einen großen Cache-Speichersatz erfordert, um rechtzeitig auf den Befehl zu reagieren.

- Die vollständigen Funktionen, Fähigkeiten und Vorteile von RISC hängen hauptsächlich von der Architektur ab.

Anwendungen

Das Anwendungen des RISC V Prozessor füge folgendes hinzu.

- RISC-V wird in eingebetteten Systemen, künstlicher Intelligenz und maschinellem Lernen verwendet.

- Diese Prozessoren werden in hochleistungsbasierten eingebetteten Systemanwendungen verwendet.

- Dieser Prozessor eignet sich für den Einsatz in bestimmten Bereichen wie Edge-Computing, KI- und Speicheranwendungen.

- RISC-V ist wichtig, da es kleineren Geräteherstellern ermöglicht, Hardware zu entwickeln, ohne dafür zu bezahlen.

- Dieser Prozessor ermöglicht es den Forschern und Entwicklern einfach, mit einer frei verfügbaren ISA- oder Befehlssatzarchitektur zu entwerfen und zu forschen.

- Die Anwendungen von RISC V reichen von kleinen eingebetteten Mikrocontrollern bis hin zu Desktop-PCs und Supercomputern einschließlich Vektorprozessoren.

Das ist also eine Übersicht über einen RISC V Prozessor – Architektur, Arbeiten mit Anwendungen. Hier ist eine Frage an Sie: Was ist ein CISC-Prozessor?