Der MOS-Transistor ist das grundlegendste Element beim Design großintegrierter Schaltungen. Diese Transistoren werden allgemein in zwei Typen PMOS und NMOS eingeteilt. Die Kombination von NMOS- und PMOS-Transistoren ist als bekannt CMOS-Transistor . Der Unterschied logische Gatter & andere implementierte digitale Logikbausteine müssen PMOS-Logik aufweisen. Diese Technologie ist kostengünstig und hat eine gute Störfestigkeit. Dieser Artikel behandelt einen der Typen von MOS-Transistoren wie einen PMOS-Transistor.

Was ist ein PMOS-Transistor?

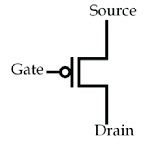

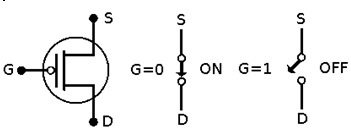

Der PMOS-Transistor oder P-Kanal-Metalloxid-Halbleiter ist eine Art Transistor, bei dem die p-Typ-Dotierstoffe in dem Kanal- oder Gate-Bereich verwendet werden. Dieser Transistor ist genau das Gegenteil des NMOS-Transistors. Diese Transistoren haben drei Hauptanschlüsse; Source, Gate und Drain, wobei die Source des Transistors mit einem Substrat vom p-Typ und der Drain-Anschluss mit einem Substrat vom n-Typ ausgelegt ist. In diesem Transistor sind die Ladungsträger wie Löcher für die Stromleitung verantwortlich. Die PMOS-Transistorsymbole sind unten gezeigt.

Wie funktioniert ein PMOS-Transistor?

Der Transistor vom p-Typ arbeitet ganz entgegengesetzt zum Transistor vom n-Typ. Dieser Transistor bildet immer dann einen offenen Stromkreis, wenn er eine nicht vernachlässigbare Spannung erhält, was bedeutet, dass kein Strom vom Gate-Anschluss (G) zur Source (S) fließt. In ähnlicher Weise bildet dieser Transistor einen geschlossenen Stromkreis, wenn er eine Spannung von etwa 0 Volt erhält, was bedeutet, dass der Strom vom Gate-Anschluss (G) zum Drain (D) fließt.

Diese Blase wird auch als Inversionsblase bezeichnet. Die Hauptfunktion dieses Kreises besteht also darin, den Eingangsspannungswert zu invertieren. Wenn der Gate-Anschluss eine 1-Spannung liefert, ändert dieser Inverter diese in Null und betreibt die Schaltung entsprechend. Die Funktion des PMOS-Transistors und des NMOS-Transistors ist also ziemlich entgegengesetzt. Sobald wir sie zu einer einzigen MOS-Schaltung zusammengeführt haben, wird daraus eine CMOS-Schaltung (Complementary Metal-Oxide Semiconductor).

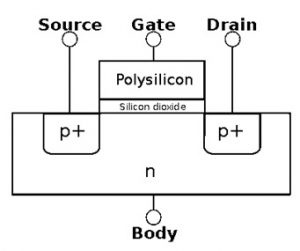

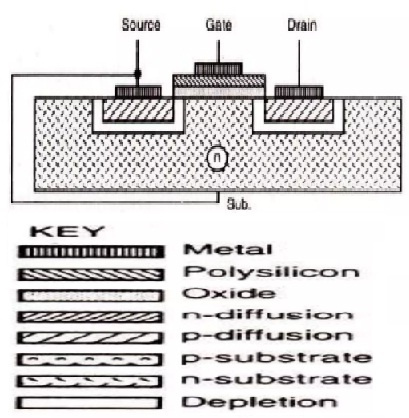

Querschnitt des PMOS-Transistors

Der Querschnitt des PMOS-Transistors ist unten gezeigt. Ein pMOS-Transistor ist mit einem Körper vom n-Typ aufgebaut, der zwei Halbleiterbereiche vom p-Typ enthält, die an das Gate angrenzen. Dieser Transistor hat ein Steuergate, wie im Diagramm gezeigt, das den Elektronenfluss zwischen den beiden Anschlüssen wie Source und Drain steuert. Beim pMOS-Transistor wird der Körper auf +ve Spannung gehalten. Sobald der Gate-Anschluss positiv ist, sind die Source- und Drain-Anschlüsse in Sperrrichtung vorgespannt. Sobald dies geschieht, fließt kein Strom mehr, sodass der Transistor ausgeschaltet wird.

Sobald die Spannungsversorgung am Gate-Anschluss abgesenkt wird, werden positive Ladungsträger zum Boden der Si-SiO2-Grenzfläche angezogen. Immer wenn die Spannung ausreichend niedrig wird, wird der Kanal invertiert und erzeugt einen leitenden Pfad vom Source-Anschluss zum Drain, indem er den Stromfluss zulässt.

Wann immer diese Transistoren mit digitaler Logik zu tun haben, haben sie normalerweise nur zwei verschiedene Werte wie 1 & 0 (EIN und AUS). Die positive Spannung des Transistors ist als VDD bekannt, die den logisch hohen Wert (1) in digitalen Schaltungen darstellt. Die VDD-Spannung steigt an TTL-Logik waren im Allgemeinen um 5V. Gegenwärtig können Transistoren solch hohen Spannungen eigentlich nicht standhalten, da sie typischerweise zwischen 1,5 V und 3,3 V liegen. Die Niederspannung wird häufig als GND oder VSS bezeichnet. VSS bedeutet also die logische „0“ und wird normalerweise auch auf 0 V gesetzt.

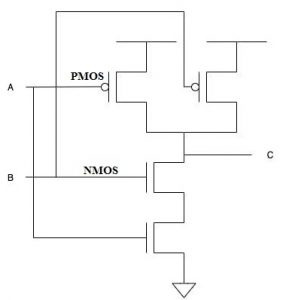

PMOS-Transistorschaltung

Das Design des NAND-Gatters unter Verwendung des PMOS-Transistors und des NMOS-Transistors ist unten gezeigt. Im Allgemeinen ist ein NAND-Gatter in der digitalen Elektronik ein Logikgatter, das auch als NICHT-UND-Gatter bezeichnet wird. Der Ausgang dieses Gatters ist nur dann niedrig (0), wenn die beiden Eingänge hoch (1) sind, und sein Ausgang ist ein Komplement zu einem UND-Gatter. Wenn einer der beiden Eingänge NIEDRIG (0) ist, werden hohe Ausgangsergebnisse erzielt.

Wenn in der folgenden Logikschaltung der Eingang A 0 und B 0 ist, dann erzeugt ein Eingang von pMOS „1“ und ein Eingang von nMOS „0“. Dieses Logikgatter erzeugt also eine logische „1“, weil es durch einen geschlossenen Stromkreis mit der Quelle verbunden und durch einen offenen Stromkreis von GND getrennt ist.

Wenn A „0“ und „B“ „1“ ist, dann erzeugt ein Eingang von pMOS eine „1“ und ein Eingang von NMOS eine „0“. Somit erzeugt dieses Gate eine logische Eins, da es über einen geschlossenen Stromkreis mit der Quelle verbunden und durch einen offenen Stromkreis von GND getrennt ist. Wenn A „1“ und B „0“ ist, dann erzeugt der „B“-Eingang von pMOS einen hohen Ausgang (1) und der „B“-Eingang von NMOS erzeugt einen niedrigen Ausgang (0). Dieses Logikgatter erzeugt also eine logische 1, da es über einen geschlossenen Stromkreis mit der Quelle verbunden und durch einen offenen Stromkreis von GND getrennt ist.

Wenn A „1“ und B „1“ ist, dann erzeugt ein Eingang von „pMOS“ eine Null und ein Eingang von nMOS „1“. Folglich sollten wir auch den B-Eingang von pMOS & nMOS überprüfen. Der B-Eingang von pMOS erzeugt eine „0“ und der B-Eingang von nMOS erzeugt eine „1“. Dieses Logikgatter erzeugt also eine logische „0“, da es durch einen offenen Stromkreis von der Quelle getrennt und über einen geschlossenen Stromkreis mit GND verbunden ist.

Wahrheitstabelle

Die Wahrheitstabelle der obigen Logikschaltung ist unten angegeben.

|

EIN |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Die Schwellenspannung des PMOS-Transistors ist normalerweise die „Vgs“, die notwendig ist, um den Kanal zu erzeugen, der als Kanalinversion bekannt ist. Bei einem PMOS-Transistor werden das Substrat und die Source-Anschlüsse einfach mit „Vdd“ verbunden. Wenn wir beginnen, die Spannung in Bezug auf den Source-Anschluss am Gate-Anschluss von Vdd bis zu einem Punkt zu reduzieren, an dem Sie die Kanalinversion bemerken, an dieser Position, wenn Sie Vgs & Source auf dem hohen Potenzial analysieren, erhalten Sie einen negativen Wert. Somit hat der PMOS-Transistor einen negativen Vth-Wert.

PMOS-Herstellungsprozess

Die bei der Herstellung von PMOS-Transistoren beteiligten Schritte werden unten erörtert.

Schritt 1:

Eine dünne Siliziumwaferschicht wird durch einfaches Dotieren von Phosphormaterial in N-Typ-Material umgewandelt.

Schritt 2:

Auf einem kompletten p-leitenden Substrat wird eine dicke Schicht aus Siliziumdioxid (Sio2) aufgewachsen.

Schritt 3:

Nun wird die Oberfläche über der dicken Siliziumdioxidschicht mit einem Fotolack beschichtet.

Schritt 4:

Danach wird diese Schicht einfach durch eine Maske mit UV-Licht belichtet, die diejenigen Bereiche definiert, in die zusammen mit Transistorkanälen diffundiert werden soll.

Schritt 5:

Diese Bereiche werden gemeinsam mit dem darunterliegenden Siliziumdioxid weggeätzt, so dass die Oberfläche des Wafers innerhalb des durch die Maske definierten Fensters freigelegt wird.

Schritt 6:

Der verbleibende Fotolack wird abgelöst und eine dünne Sio2-Schicht wird typischerweise 0,1 Mikrometer über die gesamte Oberfläche des Chips aufgewachsen. Danach wird Polysilizium darüber platziert, um die Struktur des Gates zu bilden. Ein Photoresist wird über die gesamte Polysiliziumschicht gelegt und belichtet UV-Licht durch die Maske2.

Schritt 7:

Diffusionen werden durch Erhitzen des Wafers auf maximale Temperatur und Durchleiten von Gas mit gewünschten p-Typ-Verunreinigungen wie Bor erreicht.

Schritt8:

Ein 1 Mikrometer dickes Siliziumdioxid wird gezüchtet und Photoresistmaterial wird darauf abgeschieden. Setzen Sie das ultraviolette Licht mit mask3 auf die bevorzugten Bereiche von Gate, Source und Drain, die geätzt werden, um die Kontaktschnitte vorzunehmen.

Schritt 9:

Nun wird ein Metall oder Aluminium auf seiner 1 Mikrometer dicken Oberfläche abgeschieden. Wiederum wird ein Photoresistmaterial über das gesamte Metall gezüchtet und das UV-Licht durch die Maske 4 belichtet, die geätzt wird, um das erforderliche Verbindungsdesign zu bilden. Die endgültige PMOS-Struktur ist unten gezeigt.

Eigenschaften von PMOS-Transistoren

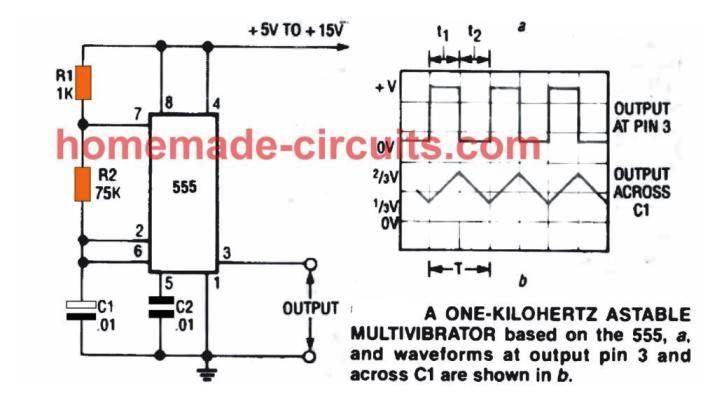

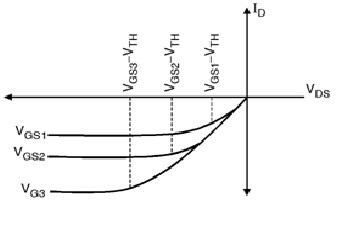

Die I-V-Eigenschaften des PMOS-Transistors sind unten gezeigt. Diese Eigenschaften sind in zwei Bereiche unterteilt, um die Beziehung zwischen dem Drain-zu-Source-Strom (IDS) sowie seinen Anschlussspannungen wie lineare und Sättigungsbereiche zu erhalten.

In einem linearen Bereich steigt der IDS linear an, wenn die VDS (Drain-zu-Source-Spannung) erhöht wird, während im Sättigungsbereich der IDS stabil und unabhängig von VDS ist. Die Hauptbeziehung zwischen dem ISD (Source-to-Drain-Strom) und seinen Anschlussspannungen wird durch ein ähnliches Verfahren des NMOS-Transistors abgeleitet. In diesem Fall ändert sich lediglich, dass die innerhalb der Inversionsschicht vorhandenen Ladungsträger einfach Löcher sind. Wenn sich die Löcher von Source zu Drain bewegen, ist auch der Stromfluss derselbe.

Somit erscheint das negative Vorzeichen innerhalb der aktuellen Gleichung. Außerdem sind alle angelegten Vorspannungen an den Anschlüssen der Vorrichtung negativ. Die ID-VDS-Eigenschaften des PMOS-Transistors sind unten dargestellt.

Die Drainstromgleichung für PMOS-Transistoren im linearen Bereich lautet:

ID = – MP Cox

Ebenso wird die Drain-Stromgleichung für PMOS-Transistoren im Sättigungsbereich wie folgt angegeben:

ID = – mp Cox (VSG – | V TH |p )^2

Wobei „mp“ die Mobilität des Lochs ist & „|VTH| p’ ist die Schwellenspannung des PMOS-Transistors.

In der obigen Gleichung zeigt das negative Vorzeichen an, dass die ID( Stromverbrauch ) fließt vom Drain (D) zur Source (S), während Löcher in die entgegengesetzte Richtung fließen. Wenn die Beweglichkeit des Lochs im Vergleich zur Elektronenbeweglichkeit niedrig ist, dann leiden PMOS-Transistoren unter der Fähigkeit der Niederstromansteuerung.

Hier geht es also um einen Überblick über PMOS-Transistoren oder p-Typ-MOS-Transistoren – Herstellung, Schaltung und ihre Funktionsweise. PMOS Transistoren ausgelegt sind mit p-Source, n-Substrat & Drain. Die Ladungsträger von PMOS sind Löcher. Dieser Transistor leitet, sobald am Gate-Anschluss eine niedrige Spannung anliegt. PMOS-basierte Geräte sind im Vergleich zu NMOS-Geräten weniger störanfällig. Diese Transistoren können als spannungsgesteuerte Widerstände, aktive Lasten, Stromspiegel, Transimpedanzverstärker und auch in Schaltern und Spannungsverstärkern verwendet werden. Hier ist eine Frage an Sie: Was ist ein NMOS-Transistor?