Das Erhöhen der Ausführungsgeschwindigkeit des Programms erhöht folglich die Geschwindigkeit von der Prozessor. Es gibt viele Möglichkeiten, sowohl die Hardware-Implementierung als auch die Softwarearchitektur, um die Ausführungsgeschwindigkeit zu erhöhen. Es wurde beobachtet, dass durch gleichzeitiges Ausführen von Anweisungen die für die Ausführung erforderliche Zeit reduziert werden kann. Das Konzept der Parallelität in Programmierung wurde vorgeschlagen. Demnach kann mehr als ein Befehl pro Taktzyklus ausgeführt werden. Dieses Konzept kann von einem Programmierer durch verschiedene Techniken wie z Pipelining, mehrere Ausführungseinheiten und mehrere Kerne . Unter all diesen Parallelitätsmethoden wird am häufigsten Pipelining praktiziert. Wie kann eine Anweisung in der Pipelining-Methode ausgeführt werden? Wie erhöht es die Ausführungsgeschwindigkeit?

Was ist Pipelining?

Um das Konzept des Pipelining zu verstehen, schauen wir uns die Stammebene an, wie das Programm ausgeführt wird. Der Befehl ist das kleinste Ausführungspaket eines Programms. Jede Anweisung enthält eine oder mehrere Operationen. Einfache Skalarprozessoren führen einen oder mehrere Befehle pro Taktzyklus aus, wobei jeder Befehl nur eine Operation enthält. Anweisungen werden als eine Folge von Phasen ausgeführt, um die erwarteten Ergebnisse zu erzielen. Diese Reihenfolge ist unten angegeben

Befehlsausführungssequenz

- IF: Ruft den Befehl in das Befehlsregister ab.

- ID: Instruction Decode, decodiert die Anweisung für den Opcode.

- AG: Adressgenerator, generiert die Adresse.

- DF: Data Fetch, ruft die Operanden in das Datenregister ab.

- EX: Ausführung, führt die angegebene Operation aus.

- WB: Schreiben Sie zurück, schreibt das Ergebnis zurück an das Register.

Nicht alle Anweisungen erfordern alle oben genannten Schritte, die meisten jedoch. Diese Schritte verwenden unterschiedliche Hardwarefunktionen. Beim Pipelining werden diese verschiedenen Phasen gleichzeitig durchgeführt. Beim Pipelining werden diese Phasen als unabhängig zwischen verschiedenen Vorgängen betrachtet und können sich überlappen. Somit können mehrere Operationen gleichzeitig ausgeführt werden, wobei sich jede Operation in ihrer eigenen unabhängigen Phase befindet.

Anleitung Pipelining

Schauen wir uns an, wie Anweisungen im Pipelining verarbeitet werden. Dies kann anhand des folgenden Diagramms leicht verstanden werden.

Anleitung Pipelining

Angenommen, die Anweisungen sind unabhängig. In einem einfachen Pipelining-Prozessor gibt es zu einem bestimmten Zeitpunkt nur eine Operation in jeder Phase. Die Anfangsphase ist die ZF-Phase. Beim ersten Taktzyklus wird also eine Operation abgerufen. Wenn der nächste Taktimpuls eintrifft, geht die erste Operation in die ID-Phase und lässt die ZF-Phase leer. Diese leere Phase wird nun der nächsten Operation zugeordnet. Während des zweiten Taktimpulses befindet sich die erste Operation in der ID-Phase und die zweite Operation in der ZF-Phase.

Für den dritten Zyklus befindet sich die erste Operation in der AG-Phase, die zweite Operation in der ID-Phase und die dritte Operation in der ZF-Phase. Auf diese Weise werden Befehle gleichzeitig ausgeführt und nach sechs Zyklen gibt der Prozessor einen vollständig ausgeführten Befehl pro Taktzyklus aus.

Wurde dieser Befehl nacheinander ausgeführt, muss zunächst der erste Befehl alle Phasen durchlaufen, dann wird der nächste Befehl abgerufen? Für die Ausführung jedes Befehls würde der Prozessor also sechs Taktzyklen benötigen. Da in einem Pipeline-Prozessor die Ausführung von Befehlen gleichzeitig erfolgt, erfordert nur der anfängliche Befehl sechs Zyklen, und alle verbleibenden Befehle werden als einer pro Zyklus ausgeführt, wodurch die Ausführungszeit verringert und die Geschwindigkeit des Prozessors erhöht wird.

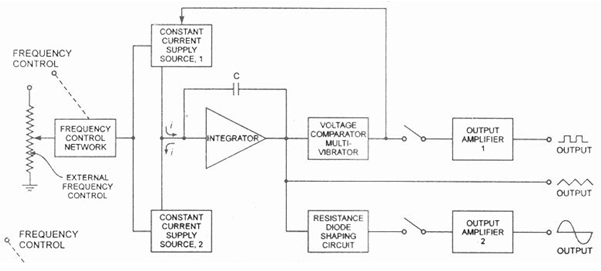

Pipelining-Architektur

Parallelität kann mit Hardware-, Compiler- und Softwaretechniken erreicht werden. Das Konzept des Pipelining in nutzen Rechnerarchitektur Viele Prozessoreinheiten sind miteinander verbunden und funktionieren gleichzeitig. In der Pipeline-Prozessorarchitektur sind separate Verarbeitungseinheiten für Ganzzahlen und Gleitkommaanweisungen vorgesehen. Während in der sequentiellen Architektur eine einzige Funktionseinheit bereitgestellt wird.

Pipeline-Prozessoreinheit

Beim statischen Pipelining sollte der Prozessor den Befehl unabhängig von der Anforderung des Befehls durch alle Phasen der Pipeline leiten. In einem dynamischen Pipeline-Prozessor kann ein Befehl die Phasen abhängig von seiner Anforderung umgehen, muss sich jedoch in sequentieller Reihenfolge bewegen. In einem komplexen dynamischen Pipeline-Prozessor kann der Befehl die Phasen umgehen und die Phasen nicht in der richtigen Reihenfolge auswählen.

Pipelining in RISC-Prozessoren

Die beliebtesten RISC-Architektur Der ARM-Prozessor folgt einem 3-stufigen und einem 5-stufigen Pipelining. Beim dreistufigen Pipelining sind die Stufen: Abrufen, Dekodieren und Ausführen. Dieses Pipelining hat eine Latenz von 3 Zyklen, da ein einzelner Befehl 3 Taktzyklen benötigt, um abgeschlossen zu werden.

ARM 3-stufiges Pipelining

Für eine ordnungsgemäße Implementierung des Pipelining sollte auch die Hardwarearchitektur aktualisiert werden. Die Hardware für das dreistufige Pipelining umfasst eine Registerbank, eine ALU, einen Barrel Shifter, einen Adressgenerator, einen Inkrementierer, einen Befehlsdecoder und Datenregister.

ARM 3 Stage Pipelining-Datenpfad

In 5 Stufen Pipelining sind die Stufen: Abrufen, Dekodieren, Ausführen, Puffer / Daten und Zurückschreiben.

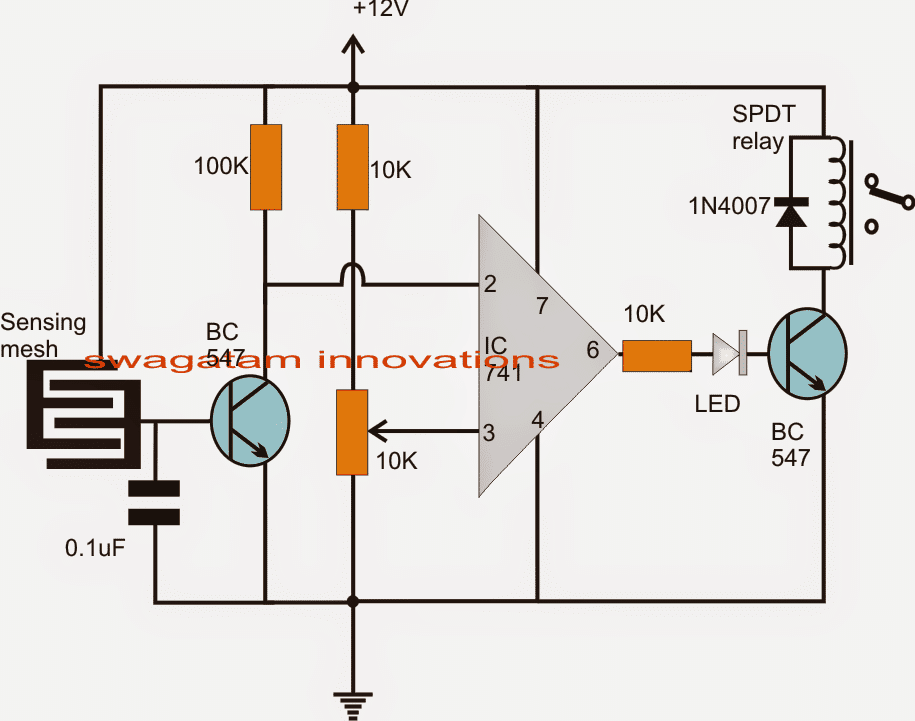

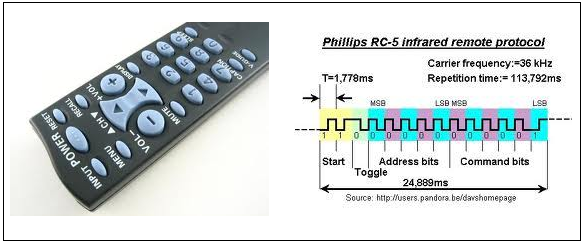

Pipelining-Gefahren

In einem typischen Computerprogramm gibt es neben einfachen Anweisungen Verzweigungsbefehle, Interrupt-Operationen, Lese- und Schreibbefehle. Pipelining ist nicht für alle Arten von Anweisungen geeignet. Wenn einige Anweisungen im Pipelining ausgeführt werden, können sie die Pipeline blockieren oder vollständig spülen. Diese Art von Problemen, die beim Pipelining verursacht werden, werden als Pipelining-Gefahren bezeichnet.

In den meisten Computerprogrammen wird das Ergebnis eines Befehls vom anderen Befehl als Operand verwendet. Wenn solche Befehle im Pipelining ausgeführt werden, tritt eine Störung auf, da das Ergebnis des ersten Befehls nicht verfügbar ist, wenn Befehl zwei mit dem Sammeln von Operanden beginnt. Befehl zwei muss also stehen bleiben, bis Befehl eins ausgeführt wird und das Ergebnis generiert wird. Diese Art von Gefahr wird als Read-After-Write-Pipelining-Gefahr bezeichnet.

Read After Write Pipelining-Gefahr

Die Ausführung von Verzweigungsanweisungen verursacht auch eine Pipelining-Gefahr. Verzweigungsanweisungen während der Ausführung im Pipelining bewirkt die Abrufphasen der nächsten Anweisungen.

Pipelined Branch-Verhalten

Vorteile von Pipelining

- Der Befehlsdurchsatz steigt.

- Durch Erhöhen der Anzahl der Pipeline-Stufen wird die Anzahl der gleichzeitig ausgeführten Anweisungen erhöht.

- Eine schnellere ALU kann entworfen werden, wenn Pipelining verwendet wird.

- Pipeline-CPUs arbeiten mit höheren Taktfrequenzen als der RAM.

- Pipelining erhöht die Gesamtleistung der CPU.

Nachteile des Pipelining

- Das Design des Pipeline-Prozessors ist komplex.

- Die Befehlslatenz erhöht sich bei Pipeline-Prozessoren.

- Der Durchsatz eines Pipeline-Prozessors ist schwer vorherzusagen.

- Je länger die Pipeline ist, desto schlimmer ist das Problem der Gefährdung von Zweiganweisungen.

Pipelining kommt allen Anweisungen zugute, die einer ähnlichen Abfolge von Ausführungsschritten folgen. Prozessoren mit komplexen Anweisungen, bei denen sich jede Anweisung anders verhält, sind schwer zu leiten. Prozessoren haben vernünftige Geräte mit 3 oder 5 Stufen der Pipeline, da mit zunehmender Tiefe der Pipeline die damit verbundenen Gefahren zunehmen. Nennen Sie einige der Pipeline-Prozessoren mit ihrer Pipeline-Phase?