Die ECL (emittergekoppelte Logik) wurde erstmals im August 1956 von Hannon S. Yourke bei IBM erfunden. Diese Logik ist auch als Strommoduslogik bekannt und wird in den Computern von IBM 7090 und 7094 verwendet. Die ECL-Familie ist im Vergleich dazu sehr schnell digitale Logik Familien. Im Allgemeinen bietet diese Logikfamilie eine Ausbreitungsverzögerung von weniger als 1 ns. Es ist eine Logikfamilie, die auf Bipolartransistoren basiert. Es ist die schnellste Logikfamilienschaltung, die zum Entwerfen eines herkömmlichen Logiksystems zugänglich ist. Dieser Artikel enthält eine Übersicht über eine Emittergekoppelte Logikschaltung , Arbeiten mit Anwendungen.

Was ist emittergekoppelte Logik?

Emittergekoppelte Logik ist die beste BJT -basierte Logikfamilie, die im konventionellen Logiksystemdesign verwendet wird. Manchmal wird es auch als Strommoduslogik bezeichnet, was eine sehr schnelle digitale Technologie ist. Im Allgemeinen wird ECL als der schnellste Logik-IC angesehen, wo er seinen Hochgeschwindigkeitsbetrieb erreicht, indem er einen sehr kleinen Spannungshub verwendet und auch verhindert, dass die Transistoren in den Sättigungsbereich gelangen.

Eine Implementierung von ECL verwendet eine positive Versorgungsspannung, die als PECL oder positiv referenzierte ECL bekannt ist. In frühen ECL-Gattern wird aufgrund der Störfestigkeit eine negative Spannungsversorgung verwendet. Danach wurde positiv referenzierte ECL aufgrund ihrer kompatibleren Logikpegel im Vergleich zu TTL-Logikfamilien sehr berühmt.

Die emittergekoppelte Logik leitet eine große Menge an statischer Energie ab, jedoch ist ihr Gesamtstromverbrauch im Vergleich dazu gering CMOS bei hohen Frequenzen. Daher ist ECL hauptsächlich in Taktverteilungsschaltungen und hochfrequenzbasierten Anwendungen von Vorteil.

Merkmale der emittergekoppelten Logik

Die Eigenschaften von ECL werden sie in vielen hochleistungsbasierten Anwendungen einsetzen.

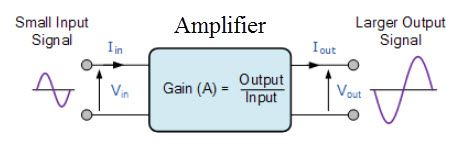

- ECL stellt zwei Ausgänge zur Verfügung, die immer komplementär zueinander sind, da der Betrieb der Schaltung auf einem Differenzverstärker basiert.

- Diese Logikfamilie ist hauptsächlich für monolithische Herstellungsverfahren geeignet, da Logikpegel eine Funktion von Widerstandsverhältnissen sind.

- Die Geräte der ECL-Familie erzeugen die richtige und komplementäre Ausgabe der vorgeschlagenen Funktion, ohne externe Inverter zu verwenden. Folglich verringert es die Paketanzahl und den Leistungsbedarf und verringert auch Probleme, die durch Zeitverzögerungen auftreten.

- ECL-Geräte im Differenzverstärkerdesign bieten eine breite Leistungsflexibilität, sodass ECL-Schaltungen sowohl als digitale als auch als lineare Schaltungen verwendet werden können.

- Das Design des ECL-Gatters hat normalerweise eine hohe und niedrige Eingangsimpedanz, was äußerst förderlich für das Erreichen eines großen Fan-Out sowie der Treiberfähigkeit ist.

- ECL-Geräte erzeugen eine konstante Stromentnahme auf der Stromversorgung, um das Design der Stromversorgung zu vereinfachen.

- Die Geräte von ECL mit offenen Emitterausgängen ermöglichen ihnen einfach, Übertragungsleitungs-Treiberkapazität einzubeziehen.

Emittergekoppelte Logikschaltung

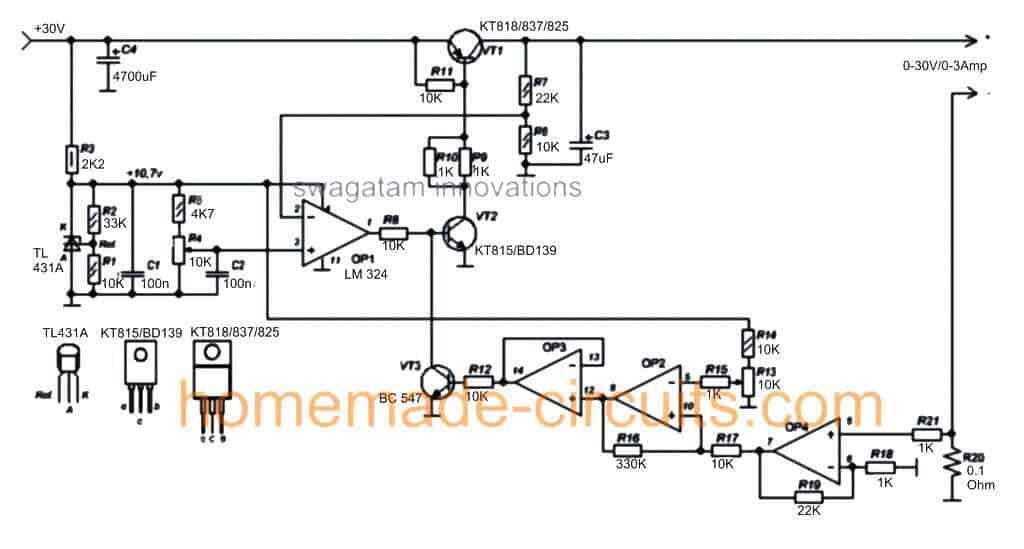

Nachfolgend ist die emittergekoppelte Logikschaltung für den Inverter dargestellt, die mit Widerständen und Transistoren aufgebaut ist. In dieser Schaltung werden die Emitteranschlüsse zweier Transistoren einfach mit dem Strombegrenzungswiderstand RE verbunden, der verwendet wird, um zu verhindern, dass der Transistor in die Sättigung eintritt. Hier wird der Ausgang des Transistors vom Kollektoranschluss statt vom Emitteranschluss abgenommen. Diese Schaltung stellt zwei Ausgänge Vout (invertierender Ausgang) und Vout2 (nicht invertierender Ausgang) und den Eingangsanschluss wie Vin bereit, wo ein hoher oder niedriger Eingang gegeben wird. +Vcc = 5V.

Wie funktioniert die emittergekoppelte Logik?

Der Betrieb der emittergekoppelten Logik besteht darin, dass immer dann, wenn der HIGH-Eingang an die ECL-Schaltung gegeben wird, der Transistor „Q1“ eingeschaltet und der Transistor Q2 ausgeschaltet wird, aber der Transistor Q1 nicht gesättigt ist. Dadurch wird der VOUT2-Ausgang auf HIGH gezogen und der Wert des VOUT1-Ausgangs wird aufgrund des Abfalls in R1 LOW sein.

Wenn der an ECL gegebene VIN-Wert LOW ist, schaltet er in ähnlicher Weise den Q1-Transistor AUS und den Q2-Transistor EIN. Der Q2-Transistor wird also nicht in die Sättigung gehen. Dadurch wird der VOUT1-Ausgang auf einen hohen Wert gezogen und der VOUT2-Ausgangswert wird aufgrund des Abfalls des R2-Widerstands niedrig.

Mal sehen, wie sich die Transistoren Q1 und Q2 ein- und ausschalten, wenn eine Spannung angelegt wird.

Die beiden Transistoren wie Q1 und Q2 in dieser Schaltung sind als Differenzverstärker durch einen gemeinsamen Emitterwiderstand verbunden.

Die Spannungsversorgungen für diese Beispielschaltung sind VCC = 5,0, VBB = 4,0 und VEE = 0 V. Die Eingangs-HIGH- und LOW-Pegelwerte sind einfach auf 4,4 V und 3,6 V definiert. Tatsächlich erzeugt diese Schaltung LOW-Ausgangs- und HIGH-Pegel, die 0,6 Volt höher sind; Dies wird jedoch in echten ECL-Schaltungen korrigiert.

Sobald Vin HIGH ist, wird der Q1-Transistor eingeschaltet, jedoch nicht gesättigt, und der Q2-Transistor wird ausgeschaltet. Die Ausgangsspannung wie VOUT2 wird also durch den Widerstand R2 auf 5 V gezogen und es kann gezeigt werden, dass der Spannungsabfall über dem Widerstand R1 etwa 0,8 V beträgt, sodass VOUT1 = 4,2 V (LOW). Außerdem VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V, da der Transistor Q1 vollständig eingeschaltet ist.

Sobald Vin LOW ist, wird der Q2-Transistor eingeschaltet, aber nicht gesättigt und der Q1-Transistor wird ausgeschaltet. Daher wird VOUT1 mit einem R1-Widerstand auf 5,0 V gezogen und es kann gezeigt werden, dass VOUT2 4,2 V beträgt. Auch VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, da der Transistor Q2 eingeschaltet ist.

Bei ECL sind die beiden Transistoren nie in Sättigung wie t Die Schwankungen der Eingangs- / Ausgangsspannung sind ziemlich klein wie 0,8 V und die Eingangsimpedanz ist hoch und der Ausgangswiderstand ist niedrig. Dadurch kann ECL schneller mit einer geringeren Verzögerungszeit für die Ausbreitung arbeiten.

Emittergekoppelte Logik-ODER/NOR-Gatterschaltung mit zwei Eingängen

Die emittergekoppelte Logik-ODER/NOR-Gatterschaltung mit zwei Eingängen ist unten gezeigt. Diese Schaltung wird entworfen, indem die obige Inverterschaltung modifiziert wird. Die Modifikation erfolgt durch Hinzufügen eines zusätzlichen Transistors auf der Eingangsseite.

Die Funktionsweise dieser Schaltung ist sehr einfach. Wenn die an beiden Transistoren Q1 und Q2 angelegten Eingänge niedrig sind, wird der Ausgang 1 (Vout1) auf einen HIGH-Wert gebracht. Diese Vout1 entspricht also dem Ausgang des NOR-Gatters.

Wenn gleichzeitig der Q3-Transistor eingeschaltet wird, wird der zweite Ausgang (Vout2) auf HIGH gesetzt. Dieser Ausgang von Vou2 entspricht also dem Ausgang des ODER-Gatters.

Wenn beide Eingänge der Q1- und Q2-Transistoren HIGH sind, werden auf die gleiche Weise die Q1- und Q2-Transistoren eingeschaltet und der niedrige Ausgang am VOUT1-Anschluss bereitgestellt.

Wenn der Q3-Transistor während dieses Vorgangs ausgeschaltet ist, liefert er eine hohe Ausgabe am VOUT2-Anschluss. Die Wahrheitstabelle für das ODER/NOR-Gatter ist unten angegeben.

|

Eingänge |

Eingänge | ODER |

NOCH |

|

EIN |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Eigenschaften der emittergekoppelten Logik

Zu den Merkmalen von ECL gehören die folgenden.

- Im Vergleich zu TTL hat ECL eine schnellere Ausbreitungszeit im Bereich von 0,5 bis 2 ns. Aber die emittergekoppelte Logik-Verlustleistung ist im Vergleich zu TTL höher, etwa 30 mW.

- Die E/A-Spannungen von ECL haben einen kleinen Hub von etwa 0,8.

- Die Eingangsimpedanz von ECL ist hoch und der Ausgangswiderstand ist niedrig; folglich ändert der Transistor seine Zustände sehr schnell.

- Die Fan-Out-Kapazität von ECLs ist hoch und die Gate-Verzögerungen sind gering.

- Die o/p-Logik von ECL wechselt von einem LOW- in einen HIGH-Zustand, aber die Spannungspegel für diese Zustände variieren zwischen TTL und EC.

- Die Störfestigkeit von ECL beträgt 0,4 V.

Vorteile und Nachteile

Das Vorteile der emittergekoppelten Logik werden unten besprochen.

- Der Fanout von ECL beträgt 25, was im Vergleich zu TTL besser und im Vergleich zu CMOS niedrig ist.

- Die durchschnittliche Ausbreitungsverzögerungszeit von ECL beträgt 1 bis 4 ns, was im Vergleich zu CMOS &

- TTL. So wird es als schnellste Logikfamilie bezeichnet.

- Wenn die BJTs im Emitter gekoppelt sind logische Gatter im aktiven Bereich arbeiten, dann haben sie im Vergleich zu allen Logikfamilien die maximale Geschwindigkeit.

- ECL-Gatter erzeugen komplementäre Ausgaben.

- Stromschaltspitzen sind in den Stromzuführungen nicht vorhanden.

- Ausgänge können gemeinsam gekoppelt werden, um die Wired-OR-Funktion bereitzustellen.

- Die Parameter von ECL ändern sich nicht wesentlich durch die Temperatur.

- Das Nein. von Funktionen, die von einem einzigen Chip zugänglich sind, ist hoch.

Das Nachteile der emittergekoppelten Logik werden unten besprochen.

- Es hat einen extrem geringeren Rauschabstand, d. h. ±200 mV.

- Die Verlustleistung ist im Vergleich zu anderen Logikgattern hoch.

- Um eine Schnittstelle mit anderen Logikfamilien herzustellen, sind Pegelumsetzer erforderlich.

- Fanout begrenzt die kapazitive Belastung.

- Verglichen mit TTL , ECL-Gatter sind teuer.

- Im Vergleich zu CMOS & TTL ist die ECL-Störfestigkeit am schlechtesten.

Anwendungen

Die Anwendungen der emittergekoppelten Logik umfassen die folgenden.

- Emittergekoppelte Logik wird als Logik- und Schnittstellentechnologie in extrem schnellen Kommunikationsgeräten wie Glasfaser-Transceiver-Schnittstellen, Ethernet- und ATM-Netzwerken (Asynchronous Transfer Mode) verwendet.

- ECL ist eine auf BJT basierende Logikfamilie, deren Hochgeschwindigkeitsbetrieb durch Verwendung eines relativ kleinen Spannungshubs und durch Vermeiden der Bewegung der Transistoren in den Sättigungsbereich erreicht werden kann.

- ECL wird zur Herstellung der ASLT-Schaltungen im IBM 360/91 verwendet.

- ECL vermeidet die Verwendung von gestapelten Transistoren, indem es eine unsymmetrische Vorspannung i/p und eine positive Rückkopplung zwischen primären und sekundären Transistoren verwendet, um eine Inverterfunktion zu erreichen.

- ECL wird in der extrem schnellen Elektronik verwendet.

Das ist also eine Übersicht über eine emittergekoppelte Logik oder ECL – Schaltung, Funktionsweise, Funktionen, Eigenschaften und Anwendungen. ECL ist im Vergleich zu anderen digitalen Logikfamilien die schnellste auf BJT basierende Logikfamilie. Es erreicht seine maximale Betriebsgeschwindigkeit, indem es einen kleinen Spannungshub verwendet und verhindert, dass sich die Transistoren in den Sättigungsbereich bewegen. Diese Logikfamilie bietet eine unglaubliche Ausbreitungsverzögerung von 1 ns, und in den neuesten ECL-Familien wird diese Verzögerung verringert. Hier ist eine Frage an Sie: Was ist ein alternativer Name für ECL?