Die Steuereinheit ist die Hauptkomponente einer Zentraleinheit (CPU) in Computern, die die Operationen während der Ausführung eines Programms durch steuern kann der Prozessor /Computer. Die Hauptfunktion der Steuereinheit besteht darin, Anweisungen aus dem Speicher eines Computers abzurufen und auszuführen. Es empfängt die Eingabeanweisung / Information vom Benutzer und wandelt sie in um Steuersignale , die dann zur weiteren Ausführung an die CPU übergeben werden. Es ist Teil der von John Neumann entwickelten Von Neumann-Architektur. Es ist für die Bereitstellung der Zeitsignale und Steuersignale verantwortlich und steuert die Ausführung eines Programms durch die CPU. Es ist als interner Bestandteil der CPU in modernen Computern enthalten. Dieser Artikel beschreibt vollständige Informationen zur Steuereinheit.

Was ist die Steuereinheit?

Die Komponente, die das Eingangssignal / die Information / die Anweisung vom Benutzer empfängt und zur Ausführung in der CPU in Steuersignale umwandelt. Es steuert und steuert den Hauptspeicher, die Arithmetik- und Logikeinheit (ALU), die Eingabe- und Ausgabegeräte und ist auch für die Anweisungen verantwortlich, die an die CPU eines Computers gesendet werden. Es holt die Anweisungen aus dem Haupterinnerung eines Prozessors und an das Prozessorbefehlsregister gesendet, das Registerinhalte enthält.

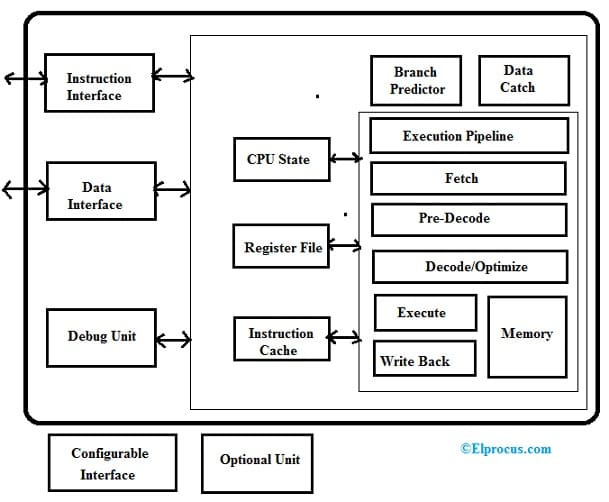

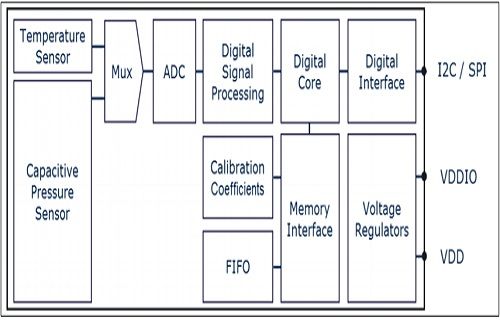

Blockschaltbild der Steuereinheit

Die Steuereinheit wandelt den Eingang in Steuersignale um und sendet ihn dann an den Prozessor und steuert die Ausführung eines Programms. Die Operationen, die ausgeführt werden müssen, werden vom Prozessor auf dem Computer gesteuert. Hauptsächlich Zentraleinheit (CPU) und Grafische Verarbeitungseinheit (GPU) benötigen eine Steuereinheit als internen Teil. Das Blockschaltbild der Steuereinheit ist oben dargestellt.

Komponenten einer Steuereinheit

Die Komponenten dieses Geräts sind Anweisungen Register , Steuersignale innerhalb der CPU, Steuersignale zum / vom Bus, Steuerbus, Eingangsflags und Taktsignale.

Die Komponenten der festverdrahteten Steuereinheit sind das Befehlsregister (enthält Opcode und Adressfeld), die Zeiteinheit und der Steuerzustand Generator , Steuersignalerzeugungsmatrix und Befehlsdecoder.

Die Komponenten der mikroprogrammierten Steuereinheit sind der nächste Adressgenerator, ein Steueradressregister, ein Steuerspeicher und ein Steuerdatenregister.

Funktionen

Das Funktionen der Steuereinheit das Folgende einschließen.

- Es steuert den Datenfluss zwischen dem Prozessor und anderen Geräten.

- Es kann die Anweisungen interpretieren und den Datenfluss im Prozessor steuern.

- Es erzeugt die Folge von Steuersignalen aus den empfangenen Befehlen oder Befehlen aus dem Befehlsregister.

- Es liegt in der Verantwortung, die Ausführungseinheiten wie ALU, Datenpuffer und Register in der CPU eines Computers zu steuern.

- Es kann Ergebnisse abrufen, dekodieren, ausführen und speichern.

- Die Daten können nicht verarbeitet und gespeichert werden

- Um die Daten zu übertragen, kommuniziert es mit den Eingabe- und Ausgabegeräten und steuert alle Einheiten des Computers.

Aufbau der Steuereinheit

Das Design kann mit zwei erfolgen Arten einer Steuereinheit die Folgendes umfassen.

- Hardwire basiert

- Mikroprogrammiert (einstufig und zweistufig)

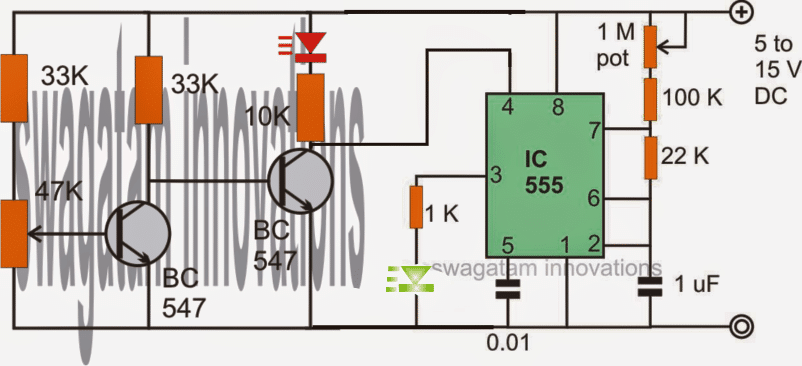

Festverdrahtete Steuereinheit

Das grundlegende Design einer festverdrahteten Steuereinheit ist oben dargestellt. Bei diesem Typ werden die Steuersignale von einer speziellen Hardware erzeugt Logikschaltung ohne Änderung in der Struktur der Schaltung. Dabei kann das erzeugte Signal nicht zur Ausführung im Prozessor modifiziert werden.

Die Grunddaten eines Opcodes (Operationscode eines Befehls wird zur Decodierung an den Befehlsdecodierer gesendet. Der Befehl Decoder ist der Satz von Decodern zum Decodieren verschiedener Datentypen im Opcode. Dies führt zu Ausgangssignalen, die Werte von aktiven Signalen enthalten, die als Eingabe an den Matrixgenerator gegeben werden, um Steuersignale für die Ausführung eines Programms durch den Prozessor des Computers zu erzeugen.

Hardwire-basierte Steuereinheit

Der Matrixgenerator liefert Zustände der Steuereinheit und die vom Prozessor ausgehenden Signale (Interrupt-Signale). Matrix ist als die gebaut programmierbares Logikarray . Die vom Matrixgenerator erzeugten Steuersignale werden als Eingabe für die nächste Generatormatrix gegeben und mit den Zeitsteuerungssignalen der Zeiteinheit kombiniert, die rechteckige Muster enthält.

Zum Abrufen eines neuen Befehls wird die Steuereinheit zu einer Anfangsstufe für die Ausführung eines neuen Befehls. Die Steuereinheit bleibt in der Anfangsstufe oder der ersten Stufe, solange die Zeitsignale, Eingangssignale und Befehlszustände eines Computers unverändert bleiben. Die Änderung des Zustands der Steuereinheit kann ausgelöst werden, wenn sich eines der erzeugten Signale ändert.

Wenn ein externes Signal oder ein Interrupt auftritt, wechselt die Steuereinheit in den nächsten Zustand und führt die Verarbeitung des Interrupt-Signals durch. Die Flags und Zustände werden verwendet, um die gewünschten Zustände auszuwählen, um den Ausführungszyklus des Befehls durchzuführen.

Im letzten Zustand ruft die Steuereinheit den nächsten Befehl ab und sendet die Ausgabe an den Programmzähler, dann an das Speicheradressregister, an das Pufferregister und dann an das Befehlsregister, um den Befehl zu lesen. Wenn der letzte Befehl (der von der Steuereinheit abgerufen wird) ein Endbefehl ist, geht er schließlich in den Betriebszustand des Prozessors über und wartet, bis der Benutzer das nächste Programm anweist.

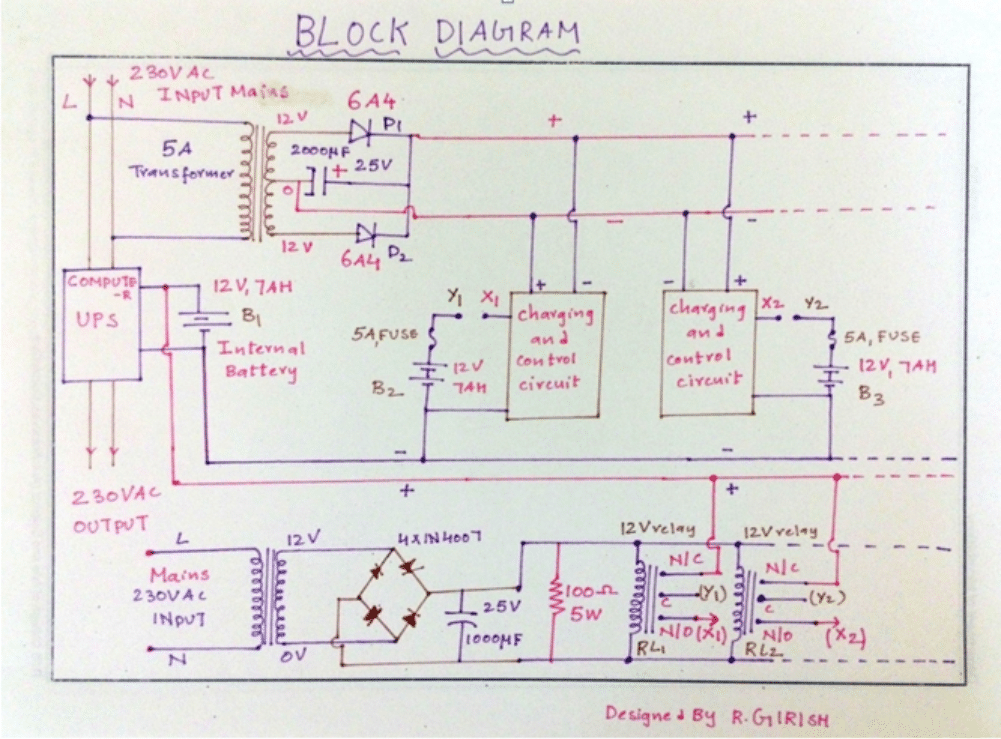

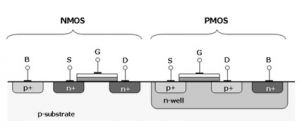

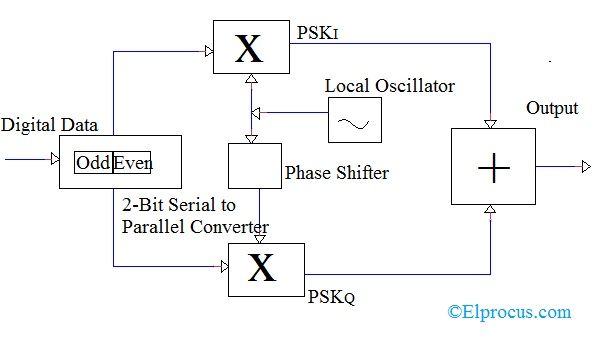

Mikroprogrammierte Steuereinheit

Bei diesem Typ wird der Steuerspeicher verwendet, um die Steuersignale zu speichern, die während der Ausführung eines Programms codiert werden. Das Steuersignal wird nicht sofort erzeugt und decodiert, da das Mikroprogramm das Adressfeld im Steuerspeicher speichert. Der gesamte Prozess ist eine Ebene.

Die Mikrooperationen werden zur Ausführung von Mikrobefehlen im Programm ausgeführt. Das Blockschaltbild der mikroprogrammierten Steuereinheit ist oben dargestellt. Aus dem Diagramm wird die Adresse des Mikrobefehls aus dem Steuerspeicher-Adressregister erhalten. Alle Informationen der Steuereinheit werden dauerhaft im Steuerspeicher ROM gespeichert.

Mikroprogrammierte Steuereinheit

Der Mikrobefehl aus dem Steuerspeicher wird vom Steuerregister gehalten. Da der Mikrobefehl in Form eines Steuerworts vorliegt (das binäre Steuerwerte enthält), müssen 1 oder mehr Mikrooperationen für die Datenverarbeitung ausgeführt werden.

Während der Ausführung von Mikrobefehlen berechnete der nächste Adressgenerator die nächste Adresse des Mikrobefehls und sendete dann an das Steueradressregister, um den nächsten Mikrobefehl zu lesen.

Die Sequenz von Mikrooperationen eines Mikroprogramms wird vom nächsten Adressgenerator ausgeführt und wirkt als Mikroprogrammsequenzer, um die Sequenzadresse zu erhalten, d. H. Aus dem Steuerspeicher zu lesen.

Verilog-Code für die Steuereinheit

Der Verilog-Code für die Steuereinheit ist unten dargestellt.

`include' prj_definition.v '

Modul CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_ADRR, MEM_RT,

// Ausgangssignale

// Ausgaben für Registerdatei

Ausgabe [`DATA_INDEX_LIMIT: 0] RF_DATA_W

Ausgabe [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

Ausgabe RF_READ, RF_WRITE

// Ausgaben für ALU

Ausgabe [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

Ausgabe [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Ausgaben für Speicher

Ausgabe [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

Ausgabe MEM_READ, MEM_WRITE

// Eingangssignale

Eingabe [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

Eingabe ZERO, CLK, RST

// Inout Signal

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Netze

wire [2: 0] proc_state

// hält den Programmzählerwert, speichert den aktuellen Befehl, Stapelzeigerregister

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] state, next_state

PROC_SM state_machine (.STATE (proc_state), CLK (CLK), RST (RST))

immer @ (posedge CLK)

Start

if (RST)

Zustand<= RST

sonst

Zustand<= next_state

Ende

immer @ (Zustand)

Start

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1'b0 ALU_OP2 = 1'b0 ALU_OPRN = 1'b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

case (state)

`PROC_FETCH: beginne

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

Ende

`PROC_DECODE: beginne

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1'b1 ALU_OP2 = 1'b1 ALU_OPRN = 1'b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

Ende

`PROC_EXE: beginne

next_state = `PROC_MEM

ALU_OP1 = 1'b1 ALU_OP2 = 1'b1 ALU_OPRN = 1'b1

RF_ADDR_R1 = 1’b0

Ende

`PROC_MEM: beginne

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

Ende

`PROC_WB: beginne

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

Ende

Endcase

Ende

Endmodul

Modul PROC_SM (STATE, CLK, RST)

// Liste der Eingaben

Eingabe CLK, RST

// Liste der Ausgänge

Ausgabe [2: 0] STATE

// Eingabeliste

Eingabe CLK, RST

// Ausgabeliste

STATE ausgeben

reg [2: 0] STATE

reg [1: 0] Zustand

reg [1: 0] next_state

reg PC_REG, INST_REG, SP_REF

`definiere PROC_FETCH 3’h0

`definiere PROC_DECODE 3’h1

`definiere PROC_EXE 3’h2

`PROC_MEM 3’h3 definieren

`PROC_WB 3’h4 definieren

// Initiierung des Zustands

Initiale

Start

state = 2’bxx

next_state = `PROC_FETCH

Ende

// Signalbehandlung zurücksetzen

immer @ (posedge RST)

Start

state = `PROC_FETCH

next_state = `PROC_FETCH

Ende

immer @ (posedge CLK)

Start

state = next_state

Ende

immer @ (Zustand)

Start

if (state === `PROC_FETCH)

Start

next_state = `PROC_DECODE

print_instruction (INST_REG)

Ende

if (state === `PROC_DECODE)

Start

next_state = `PROC_EXE

Ende

if (state === `PROC_EXE)

Start

next_state = `PROC_MEM

print_instruction (SP_REF)

Ende

if (state === `PROC_MEM)

Start

next_state = `PROC_WB

Ende

if (state === `PROC_WB)

Start

next_state = `PROC_FETCH

print_instruction (PC_REG)

Ende

Ende

Task print_instruction

Eingabe [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] Opcode

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] sofortige reg [25: 0] Adresse

Start

// analysiere die Anweisung

// R-Typ

{opcode, rs, rt, rd, shamt, funct} = inst

// Ich tippe

{opcode, rs, rt, sofort} = inst

// J-Typ

{Opcode, Adresse} = inst

$ write ('@% 6dns -> [0X% 08h]', $ time, inst)

case (opcode) // R-Typ

6'h00: Start

case (Funktion)

6'h20: $ write ('addiere r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h22: $ write ('sub r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h2c: $ write ('mul r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h24: $ write ('und r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h25: $ write ('oder r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h27: $ write ('noch r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h2a: $ write ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h00: $ write ('sll r [% 02d],% 2d, r [% 02d]', rs, shamt, rd)

6'h02: $ write ('srl r [% 02d], 0X% 02h, r [% 02d]', rs, shamt, rd)

6'h08: $ write ('jr r [% 02d]', rs)

Standard: $ write ('')

Endcase

Ende

// Ich tippe

6'h08: $ write ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h1d: $ write ('muli r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h0c: $ write ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h0d: $ write ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6’h0f: $ write ('lui r [% 02d], 0X% 04h', rt, sofort)

6'h0a: $ write ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h04: $ write ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h05: $ write ('bne r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h23: $ write ('lw r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

6'h2b: $ write ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, sofort)

// J-Typ

6'h02: $ write ('jmp 0X% 07h', Adresse)

6'h03: $ write ('jal 0X% 07h', Adresse)

6'h1b: $ write ('push')

6'h1c: $ write ('pop')

Standard: $ write ('')

Endcase

$ write (' n')

Ende

Task beenden

Endmodul

FAQs

1). Was ist die Arbeit einer Steuereinheit?

Die Arbeit der Steuereinheit besteht darin, den Datenfluss oder die Anweisungen für die Ausführung eines Computers durch den Prozessor zu steuern. Es steuert, verwaltet und koordiniert den Hauptspeicher, die ALU, die Register, die Eingabe- und Ausgabeeinheiten. Es ruft die Anweisungen ab und erzeugt Steuersignale für die Ausführung.

2). Was ist der Steuerspeicher?

Der Steuerspeicher ist normalerweise RAM oder ROM, um die Adresse und Daten des Steuerregisters zu speichern.

3). Was ist das Wilkes-Steuergerät?

Die sequentielle und Kombinationsschaltungen der festverdrahteten Steuereinheit werden durch die Wilkes-Steuereinheit ersetzt. Es verwendet eine Speichereinheit, um die Befehlssequenzen eines Mikroprogramms zu speichern.

4). Was ist eine festverdrahtete Steuereinheit?

Die festverdrahtete Steuereinheit erzeugt die Steuersignale, indem sie in jedem Taktimpuls von einem Zustand in einen anderen Zustand wechselt, ohne dass sich die Schaltung physikalisch ändert. Die Erzeugung von Steuersignalen hängt von Befehlsregister-, Decoder- und Interrupt-Signalen ab.

5). Was ist der Steuerspeicher?

Die Informationen der Steuereinheit oder Daten werden vorübergehend oder dauerhaft im Steuerspeicher gespeichert.

Es gibt zwei Arten von Steuerspeichern. Sie sind Direktzugriffsspeicher (RAM) und Nur-Lese-Speicher (ROM).

Hier geht es also um Definition, Komponenten, Design, Diagramm, Funktionen und Arten von Steuereinheiten . Hier ist eine Frage an Sie: 'Was ist der Zweck des Steueradressregisters?'