Der Begriff CMOS steht für 'Complementary Metal Oxide Semiconductor'. Dies ist eine der beliebtesten Technologien in der Computerchip-Designbranche und wird heute in großem Umfang zum Formen verwendet integrierte Schaltkreise in zahlreichen und vielfältigen Anwendungen. Heutige Computerspeicher, CPUs und Mobiltelefone nutzen diese Technologie aufgrund mehrerer entscheidender Vorteile. Diese Technologie verwendet sowohl P-Kanal- als auch N-Kanal-Halbleiterbauelemente. Eine der beliebtesten heute verfügbaren MOSFET-Technologien ist die Complementary MOS- oder CMOS-Technologie. Dies ist die dominierende Halbleitertechnologie für Mikroprozessoren, Mikrocontroller-Chips, Speicher wie RAM, ROM, EEPROM und Anwendungsspezifische integrierte Schaltkreise (ASICs).

Einführung in die MOS-Technologie

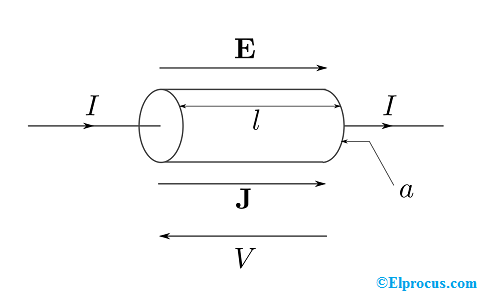

Beim IC-Design ist die grundlegende und wichtigste Komponente der Transistor. Der MOSFET ist also eine Art von Transistor, der in vielen Anwendungen verwendet wird. Die Bildung dieses Transistors kann wie ein Sandwich erfolgen, indem eine Halbleiterschicht, im Allgemeinen ein Wafer, eine Schicht aus einem Einkristall aus Silizium, eine Schicht aus Siliziumdioxid und eine Metallschicht eingeschlossen werden. Diese Schichten ermöglichen die Bildung der Transistoren innerhalb des Halbleitermaterials. Ein guter Isolator wie Sio2 hat eine dünne Schicht mit einer Dicke von hundert Molekülen.

Die Transistoren, für deren Gate-Abschnitte wir polykristallines Silizium (Poly) anstelle von Metall verwenden. Das Polysilicium-Gate des FET kann fast unter Verwendung von Metall-Gates in ICs in großem Maßstab ersetzt werden. Manchmal werden sowohl Polysilicium- als auch Metall-FETs als IGFETs bezeichnet, was isolierte Gate-FETs bedeutet, da der Sio2 unter dem Gate ein Isolator ist.

CMOS (Complementary Metal Oxide Semiconductor)

Die Haupt Vorteil von CMOS gegenüber NMOS und die BIPOLAR-Technologie ist die viel geringere Verlustleistung. Im Gegensatz zu NMOS- oder BIPOLAR-Schaltungen weist eine komplementäre MOS-Schaltung fast keine statische Verlustleistung auf. Die Leistung wird nur dann verbraucht, wenn der Stromkreis tatsächlich schaltet. Dies ermöglicht die Integration von mehr CMOS-Gattern auf einem IC als in NMOS oder bipolare Technologie , was zu einer viel besseren Leistung führt. Der komplementäre Metalloxid-Halbleitertransistor besteht aus einem P-Kanal-MOS (PMOS) und einem N-Kanal-MOS (NMOS). Weitere Informationen finden Sie unter dem Link der Herstellungsprozess des CMOS-Transistors .

CMOS (Complementary Metal Oxide Semiconductor)

NMOS

NMOS ist auf einem Substrat vom p-Typ aufgebaut, auf dem Source und Drain vom n-Typ diffundiert sind. In NMOS sind die meisten Ladungsträger Elektronen. Wenn eine hohe Spannung an das Gate angelegt wird, leitet das NMOS. In ähnlicher Weise leitet NMOS nicht, wenn eine niedrige Spannung an das Gate angelegt wird. NMOS wird als schneller als PMOS angesehen, da die Ladungsträger in NMOS, die Elektronen sind, doppelt so schnell wandern wie die Löcher.

NMOS-Transistor

PMOS

Der P-Kanal-MOSFET besteht aus einer Source und einem Drain vom P-Typ, die auf einem Substrat vom N-Typ diffundiert sind. Die meisten Träger sind Löcher. Wenn eine hohe Spannung an das Gate angelegt wird, leitet das PMOS nicht. Wenn eine niedrige Spannung an das Gate angelegt wird, leitet das PMOS. Die PMOS-Geräte sind rauschunempfindlicher als NMOS-Geräte.

PMOS-Transistor

CMOS-Arbeitsprinzip

In der CMOS-Technologie werden sowohl N- als auch P-Transistoren zum Entwerfen von Logikfunktionen verwendet. Das gleiche Signal, das einen Transistor eines Typs einschaltet, wird verwendet, um einen Transistor des anderen Typs auszuschalten. Diese Eigenschaft ermöglicht den Entwurf von Logikbausteinen mit nur einfachen Schaltern, ohne dass ein Pull-up-Widerstand erforderlich ist.

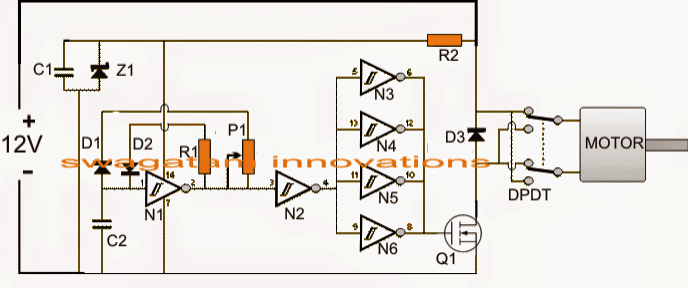

Im CMOS Logikgatter Eine Sammlung von n-Typ-MOSFETs ist in einem Pulldown-Netzwerk zwischen dem Ausgang und der Niederspannungs-Stromversorgungsschiene (Vss oder ziemlich oft Masse) angeordnet. Anstelle des Lastwiderstands von NMOS-Logikgattern weisen CMOS-Logikgatter eine Sammlung von p-Typ-MOSFETs in einem Pull-up-Netzwerk zwischen dem Ausgang und der Hochspannungsschiene (häufig als Vdd bezeichnet) auf.

CMOS mit Pull Up & Pull Down

Wenn also sowohl ein p-Typ- als auch ein n-Typ-Transistor ihre Gates an denselben Eingang angeschlossen haben, ist der p-Typ-MOSFET EIN, wenn der n-Typ-MOSFET AUS ist, und umgekehrt. Die Netzwerke sind so angeordnet, dass eines für jedes Eingabemuster EIN und das andere AUS ist, wie in der folgenden Abbildung gezeigt.

CMOS bietet relativ hohe Geschwindigkeit, geringe Verlustleistung, hohe Rauschabstände in beiden Zuständen und arbeitet über einen weiten Bereich von Quellen- und Eingangsspannungen (vorausgesetzt, die Quellenspannung ist fest). Um das Arbeitsprinzip der komplementären Metalloxidhalbleiter besser zu verstehen, müssen wir außerdem die CMOS-Logikgatter kurz erläutern, wie nachstehend erläutert.

Welche Geräte verwenden CMOS?

Technologie wie CMOS wird in verschiedenen Chips wie Mikrocontrollern, Mikroprozessoren, SRAM (statischem RAM) und anderen digitalen Logikschaltungen verwendet. Diese Technologie wird in einer Vielzahl von analogen Schaltkreisen verwendet, darunter Datenkonverter, Bildsensoren und hoch integrierte Transceiver für verschiedene Arten der Kommunikation.

CMOS-Wechselrichter

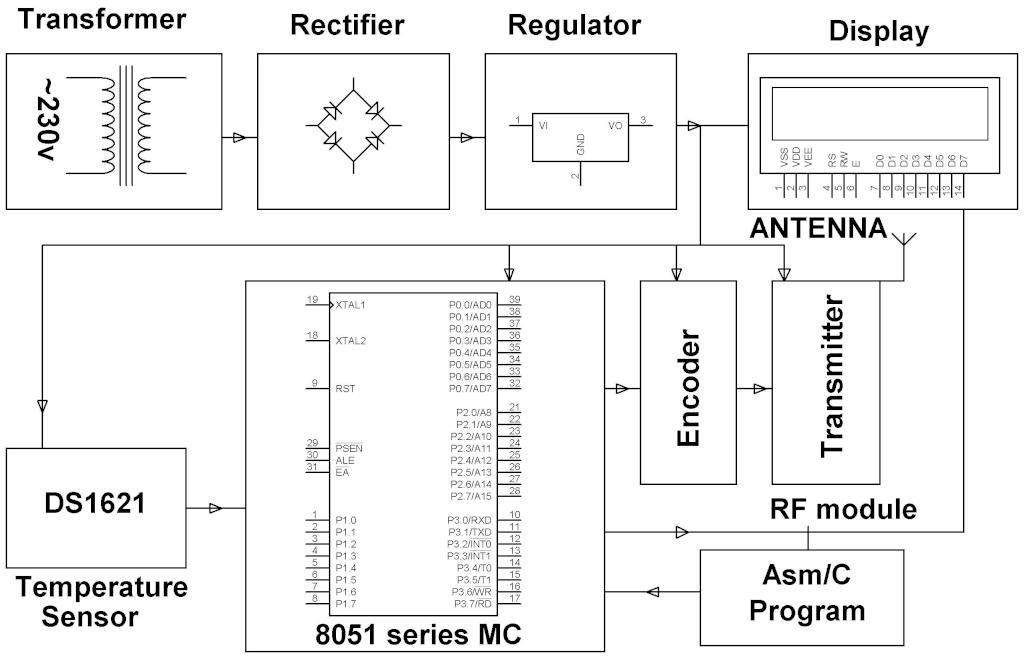

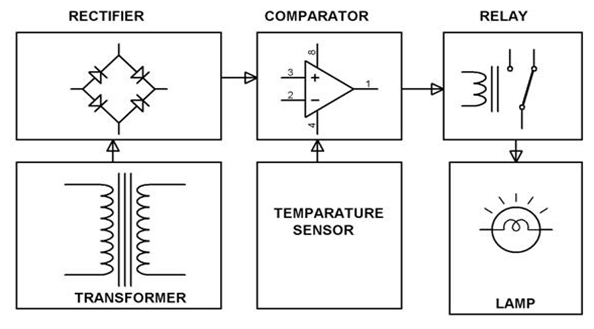

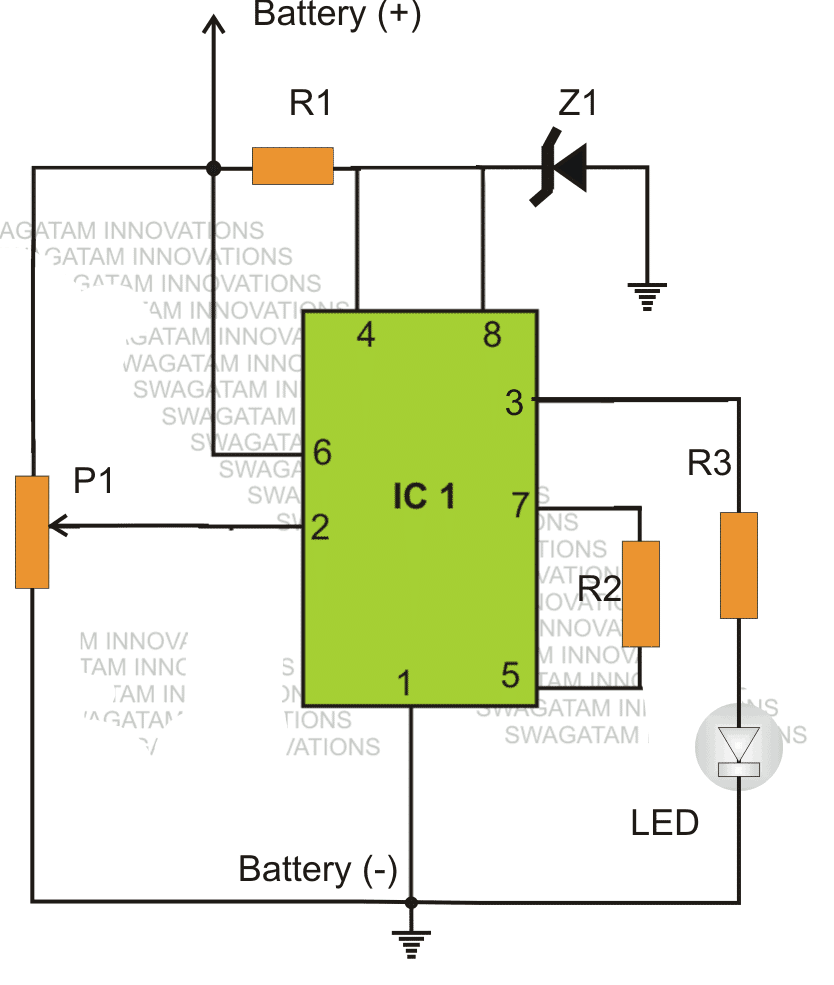

Die Wechselrichterschaltung wie in der folgenden Abbildung gezeigt. Es besteht aus PMOS- und NMOS-FET . Der Eingang A dient als Gate-Spannung für beide Transistoren.

Der NMOS-Transistor hat Eingang von Vss (Masse) und der PMOS-Transistor hat Eingang von Vdd. Der Anschluss Y wird ausgegeben. Wenn am Eingangsanschluss (A) des Wechselrichters eine Hochspannung (~ Vdd) anliegt, wird das PMOS zu einem offenen Stromkreis und das NMOS ausgeschaltet, sodass der Ausgang auf Vss heruntergezogen wird.

CMOS-Wechselrichter

Wenn eine niedrige Spannung ( Die folgende Abbildung zeigt ein komplementäres MOS-NAND-Gatter mit 2 Eingängen. Es besteht aus zwei Serien-NMOS-Transistoren zwischen Y und Masse und zwei parallelen PMOS-Transistoren zwischen Y und VDD. Wenn entweder Eingang A oder B logisch 0 ist, ist mindestens einer der NMOS-Transistoren AUS, wodurch der Pfad von Y nach Masse unterbrochen wird. Mindestens einer der pMOS-Transistoren ist jedoch eingeschaltet, wodurch ein Pfad von Y zu VDD erstellt wird. NAND-Gatter mit zwei Eingängen Daher ist der Ausgang Y hoch. Wenn beide Eingänge hoch sind, sind beide nMOS-Transistoren eingeschaltet und beide pMOS-Transistoren sind AUS. Daher ist der Ausgang logisch niedrig. Die Wahrheitstabelle des NAND-Logikgatters ist in der folgenden Tabelle angegeben. Ein NOR-Gatter mit 2 Eingängen ist in der folgenden Abbildung dargestellt. Die NMOS-Transistoren sind parallel geschaltet, um den Ausgang niedrig zu ziehen, wenn einer der Eingänge hoch ist. Die PMOS-Transistoren sind in Reihe geschaltet, um den Ausgang hoch zu ziehen, wenn beide Eingänge niedrig sind, wie in der folgenden Tabelle angegeben. Die Ausgabe bleibt niemals schwebend. NOR-Gatter mit zwei Eingängen Die Wahrheitstabelle des NOR-Logikgatters ist in der folgenden Tabelle angegeben. Die Herstellung von CMOS-Transistoren kann auf dem Wafer aus Silizium erfolgen. Der Durchmesser des Wafers reicht von 20 mm bis 300 mm. Dabei ist der Lithografieprozess der gleiche wie bei der Druckmaschine. Bei jedem Schritt können verschiedene Materialien abgeschieden, geätzt oder anders strukturiert werden. Dieser Vorgang ist sehr einfach zu verstehen, wenn sowohl die Oberseite des Wafers als auch der Querschnitt innerhalb einer vereinfachten Montagemethode betrachtet werden. Die Herstellung von CMOS kann unter Verwendung von drei Technologien erreicht werden, nämlich N-Well-Pt-P-Well, Twin-Well, ein SOI (Silicon on Insulator). Weitere Informationen finden Sie unter diesem Link CMOS-Herstellung . Die typische Lebensdauer einer CMOS-Batterie beträgt ca. 10 Jahre. Dies kann sich jedoch je nach Auslastung und Umgebung ändern, wo immer sich der PC befindet. Wenn die CMOS-Batterie ausfällt, kann der Computer nach dem Ausschalten nicht die genaue Uhrzeit und das genaue Datum auf dem Computer beibehalten. Wenn der Computer beispielsweise eingeschaltet ist, werden möglicherweise Uhrzeit und Datum wie 12:00 Uhr und der 1. Januar 1990 angezeigt. Dieser Fehler gibt an, dass die Batterie des CMOS ausgefallen ist. Die wichtigsten Merkmale von CMOS sind eine geringe statische Auslastung und eine hohe Störfestigkeit. Wenn der einzelne Transistor aus dem Paar von MOSFET-Transistoren ausgeschaltet wird, verbraucht die Reihenkombination während des Umschaltens zwischen den beiden wie EIN & AUS angegebenen eine signifikante Leistung. Infolgedessen erzeugen diese Geräte im Vergleich zu anderen Arten von Logikschaltungen wie TTL- oder NMOS-Logik, die normalerweise einen gewissen Dauerstrom verbrauchen, keine Abwärme, selbst wenn sie ihren Zustand nicht ändern. Diese CMOS-Eigenschaften ermöglichen die Integration von Logikfunktionen mit hoher Dichte in eine integrierte Schaltung. Aus diesem Grund ist CMOS die am häufigsten verwendete Technologie, die in VLSI-Chips ausgeführt wird. Der Ausdruck MOS bezieht sich auf die physikalische Struktur des MOSFET, die eine Elektrode mit einem Metallgatter enthält, das sich oben auf einem Oxidisolator aus Halbleitermaterial befindet. Ein Material wie Aluminium wird nur einmal verwendet, das Material ist jedoch jetzt Polysilicium. Das Entwerfen anderer Metallgatter kann unter Verwendung eines Comebacks durch das Eintreffen von dielektrischen Materialien mit hohem κ innerhalb des Prozesses des CMOS-Prozesses erfolgen. Die Bildsensoren wie das ladungsgekoppelte Bauelement (CCD) und der komplementäre Metalloxid-Halbleiter (CMOS) sind zwei verschiedene Arten von Technologien. Diese werden verwendet, um das Bild digital zu erfassen. Jeder Bildsensor hat seine Vor- und Nachteile und Anwendungen. Der Hauptunterschied zwischen CCD und CMOS besteht in der Art der Erfassung des Rahmens. Ein ladungsgekoppeltes Gerät wie CCD verwendet einen Global Shutter, während das CMOS einen Rolling Shutter verwendet. Diese beiden Bildsensoren wandeln die Ladung von Licht in Elektrizität um und verarbeiten sie zu elektronischen Signalen. Der in CCDs verwendete Herstellungsprozess ist speziell, um die Fähigkeit zu bilden, Ladung ohne Änderung über den IC zu bewegen. Dieser Herstellungsprozess kann also zu extrem hochwertigen Sensoren für Lichtempfindlichkeit und Wiedergabetreue führen. Im Gegensatz dazu verwenden CMOS-Chips feste Herstellungsverfahren, um den Chip zu entwerfen, und ein ähnlicher Prozess kann auch bei der Herstellung der Mikroprozessoren verwendet werden. Aufgrund der Unterschiede in der Herstellung gibt es einige deutliche Unterschiede zwischen den Sensoren wie CCD 7 CMOS. CCD-Sensoren erfassen die Bilder mit weniger Rauschen und hoher Qualität, während die CMOS-Sensoren normalerweise anfälliger für Rauschen sind. Normalerweise verbraucht CMOS weniger Strom, während das CCD viel mehr als das 100-fache des CMOS-Sensors verbraucht. Die Herstellung von CMOS-Chips kann auf jeder typischen Si-Produktionslinie erfolgen, da diese im Vergleich zu CCDs tendenziell sehr billig sind. CCD-Sensoren sind ausgereifter, weil sie über einen langen Zeitraum in Massenproduktion hergestellt werden. Sowohl die CMOS- als auch die CCD-Bildgeber hängen von der Wirkung der Lichtschranke ab, um das elektrische Signal vom Licht zu erzeugen Aufgrund der oben genannten Unterschiede werden CCDs in Kameras verwendet, um qualitativ hochwertige Bilder mit vielen Pixeln und hervorragender Lichtempfindlichkeit zu erzielen. Normalerweise haben CMOS-Sensoren eine geringere Auflösung, Qualität und Empfindlichkeit. Ein Latch-up kann definiert werden, wenn der Kurzschluss zwischen den beiden Anschlüssen wie Strom und Masse auftritt, so dass hoher Strom erzeugt und der IC beschädigt werden kann. In CMOS ist Latch-up das Auftreten einer niederohmigen Spur zwischen der Stromschiene und der Erdungsschiene aufgrund der Kommunikation zwischen den beiden Transistoren wie parasitärem PNP und NPN Transistoren . In der CMOS-Schaltung sind die beiden Transistoren wie PNP und NPN mit zwei Versorgungsschienen wie VDD und GND verbunden. Der Schutz dieser Transistoren kann durch Widerstände erfolgen. Bei einer Latch-Up-Übertragung fließt der Strom von VDD zu GND direkt durch die beiden Transistoren, so dass ein Kurzschluss auftreten kann, sodass extremer Strom von VDD zum Erdungsanschluss fließt. Es gibt verschiedene Methoden zur Verhinderung von Latch-Ups Zur Verhinderung von Latch-Ups kann ein hoher Widerstand in die Spur eingebracht werden, um den Stromfluss während der gesamten Versorgung zu stoppen und β1 * β2 unter Verwendung der folgenden Methoden unter 1 zu bringen. Die Struktur des parasitären SCR wird in der Umgebung von Transistoren wie PMOS & NMOS durch eine isolierende Oxidschicht abgetrennt. Die Technologie für den Verriegelungsschutz schaltet das Gerät aus, sobald eine Verriegelung bemerkt wird. Die Testservices von Latch-up können von vielen Anbietern auf dem Markt durchgeführt werden. Dieser Test kann durch eine Folge von Versuchen durchgeführt werden, die Struktur des SCR im CMOS-IC zu aktivieren, während die zugehörigen Pins überprüft werden, wenn Überstrom durch diesen fließt. Es wird empfohlen, die ersten Proben aus der Versuchsreihe zu entnehmen und an ein Testlabor von Latch-up zu senden. In diesem Labor wird die bestmögliche Stromversorgung angewendet und anschließend die Stromversorgung der Ein- und Ausgänge des Chips bereitgestellt, wenn durch Überwachung der Stromversorgung ein Latch-up auftritt. Die Vorteile von CMOS umfassen Folgendes. Die Hauptvorteile von CMOS gegenüber TTL sind eine gute Rauschmarge sowie ein geringerer Stromverbrauch. Dies ist darauf zurückzuführen, dass keine gerade leitende Spur von VDD nach GND vorhanden ist. Die Abfallzeiten hängen von den Eingangsbedingungen ab. Dann wird die Übertragung des digitalen Signals über CMOS-Chips einfach und kostengünstig. CMOS wird verwendet, um die Speichermenge auf der Hauptplatine des Computers zu erläutern, die in den Einstellungen des BIOS gespeichert wird. Diese Einstellungen umfassen hauptsächlich Datum, Uhrzeit und Einstellungen der Hardware Die Ausgänge, wenn CMOS aktiv in beide Richtungen fahren Die Nachteile von CMOS umfassen die folgenden. Komplementäre MOS-Prozesse waren weit verbreitet und haben NMOS- und bipolare Prozesse für nahezu alle digitalen Logikanwendungen grundlegend ersetzt. Die CMOS-Technologie wurde für die folgenden digitalen IC-Designs verwendet. Und so kam es dass der CMOS-Transistor ist sehr berühmt weil sie elektrische Energie effizient nutzen. Sie verwenden keine Stromversorgung, wenn sie von einem Zustand in einen anderen wechseln. Außerdem arbeiten die komplementären Halbleiter gegenseitig, um die O / P-Spannung zu stoppen. Das Ergebnis ist ein stromsparendes Design, das weniger Wärme liefert. Aus diesem Grund haben diese Transistoren andere frühere Designs wie CCDs in Kamerasensoren geändert und werden in den meisten aktuellen Prozessoren verwendet. Der Speicher des CMOS in einem Computer ist eine Art nichtflüchtiger RAM, in dem die BIOS-Einstellungen sowie die Informationen zu Uhrzeit und Datum gespeichert sind. Ich glaube, Sie haben ein besseres Verständnis für dieses Konzept. Darüber hinaus Fragen zu diesem Konzept oder Elektronikprojekte Bitte geben Sie Ihre wertvollen Vorschläge, indem Sie im Kommentarbereich unten einen Kommentar abgeben. Hier ist eine Frage für Sie, warum CMOS NMOS vorzuziehen ist. EINGANG LOGISCHER EINGANG AUSGABE LOGIKAUSGABE 0 v 0 Vdd 1 Vdd 1 0 v 0 CMOS NAND Gate

ZU B. Pulldown-Netzwerk Pull-up-Netzwerk AUSGABE Y. 0 0 AUS AUF 1 0 1 AUS AUF 1 1 0 AUS AUF 1 1 1 AUF AUS 0 CMOS NOR Gate

ZU B. Y. 0 0 1 0 1 0 1 0 0 1 1 0 CMOS-Herstellung

Eine Lebensdauer der CMOS-Batterie

Fehlersymptome der CMOS-Batterie

CMOS-Eigenschaften

CCD gegen CMOS

In einigen Anwendungen verbessern sich CMOS-Sensoren in jüngster Zeit so weit, dass sie nahezu gleichwertig mit CCD-Geräten sind. Im Allgemeinen sind CMOS-Kameras nicht teuer und haben eine hohe Lebensdauer der Batterie.Latch-Up im CMOS

Vorteile

TTL ist eine digitale Logikschaltung, bei der Bipolartransistoren mit Gleichstromimpulsen arbeiten. Mehrere Transistorlogikgatter bestehen normalerweise aus einem einzigen IC.Nachteile

CMOS-Anwendungen