In diesem Beitrag werden die Pinbelegungsfunktion und andere wichtige Spezifikationen des IC 4043 erläutert. Erfahren Sie mehr über das vollständige Datenblatt dieses sehr interessanten Chips.

Pinbelegung Datenblatt des IC 4043

Technisch gesehen ist der IC 4043 ein Quad-Set / Reset (R / S) -Latch mit 3 Logikzustandsausgängen.

Genauer gesagt verfügt dieser Chip über 4 Eingangssätze (dh 8 Eingangsbelegungen) und 4 entsprechende Einzelausgänge.

Die 4 Sätze von Eingängen bestehen aus 4 Paaren von Set / Reset-Eingängen.

Für jedes Setzen / Zurücksetzen haben wir einen entsprechenden Ausgang.

Alle diese Set-Reset-Eingänge reagieren auf hohe Logiksignale und erzeugen einen bistabilen Effekt an den entsprechenden Ausgangsbelegungen.

Bistabiler Flip / Flop

Bistabil bezieht sich auf eine Flip-Flop-Aktion, mit anderen Worten, ein hoher Impuls zum 'Set'-Eingang macht den entsprechenden Ausgang von seinem ursprünglichen niedrigen Zustand hoch, und ein hoher Impuls zum Reset-Eingang kehrt den obigen Zustand vom hohen zurück zum niedrigen Zustand zurück.

Um einen entsprechenden Ausgang hoch zu machen, müssen wir daher grundsätzlich einen hohen Wert an ihren 'Set'-Eingängen anlegen und um die Ausgänge wieder niedrig zu machen, müssen wir einfach einen weiteren hohen Wert an ihre zurückgesetzten Eingänge anlegen.

Die Funktionsweise der Eingangs- und Ausgangsbelegung ist so einfach.

Darüber hinaus verfügt der IC über eine weitere interessante Eingangs-Pinbelegung OE, bei der es sich um eine gemeinsame Ausgangs-Pinbelegung handelt.

Funktion setzen / zurücksetzen

Um die oben erläuterten Set / Reset-Aktionen im IC zu aktivieren, sollte dieser OE-Eingang mit Logic High oder einfach mit Vdd (Supply Votage) verbunden werden.

In der obigen Situation ist die Ausgabe mit der angegebenen Flip-Flop-Funktion zulässig.

Wenn der OE-Eingang mit Masse verbunden ist, friert der Ausgang ein und erzeugt eine hochohmige Antwort, die weder einen niedrigen noch einen hohen Ausgang zeigt, sondern sperrt den Eingang in einen nicht reagierenden blockierten Zustand, daher der logische Zustandsausgang mit dem Namen 3.

Somit kann der OE-Eingang verwendet werden, um die IC-Funktion herunterzufahren, wenn dies für eine bestimmte Anwendung erforderlich ist.

Der IC funktioniert am besten mit Versorgungsspannungen von 5 bis 15 V.

Fassen wir die Pinbelegungsfunktionen und -spezifikationen des IC 4043 mit den folgenden Daten zusammen:

- 1Q bis 4Q (Pins: 2, 9, 10, 1) Gepufferter 3-Zustands-Latch-Ausgang

- 1R bis 4R (Pins: 3, 7, 11, 15) Reset-Eingang (aktiv HIGH)

- 1S bis 4S (Pins: 4, 6, 12, 14) Eingang einstellen (aktiv HIGH)

- OE (Pin: 5) gemeinsamer Ausgang aktivieren Eingang

- VSS (Pin: 8) Masseversorgungsspannung

- N. C. (Pin: 13) nicht angeschlossen

- VDD (Pin: 16) Versorgungsspannung

Weitere Updates:

In diesen Beiträgen versuchen wir, die Funktionsweise des IC 4043 und des IC 4044 zu verstehen, indem wir die verschiedenen Spezifikationen, das Datenblatt der Geräte und ihre Pinbelegung untersuchen.

Grundsätzlich sind beide Varianten Quad Cross-Coupled CMOS 3-State R / S oder Reset / Set Latches. Quad bedeutet mit 4 Ausgängen, die über ein Steuereingangssignal mit einem logisch hohen Wert gesetzt oder zwischengespeichert oder durch ein nachfolgendes Eingangssignal auf logisch Null zurückgesetzt werden können.

Die 3-Zustands-Funktion ermöglicht die Steuerung der ICs mithilfe von 3-Logik

Das grundlegende Arbeitsprinzip von IC 4043 und IC 4044 ist das gleiche wie oben, der einzige Unterschied besteht darin, dass IC 4043B vierfach gekreuzte 3-Zustände sind NOCH Latch und IC 4044B sind vierfach gekreuzte 3-Zustände NAND Verriegeln.

Pinbelegung

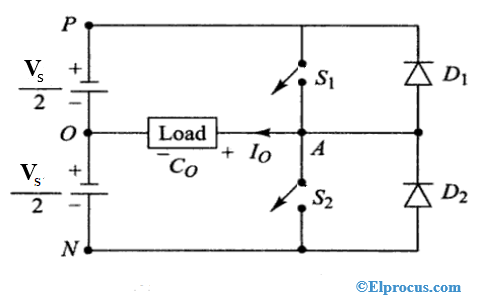

Die folgenden Pinbelegungsdiagramme der ICs zeigen die interne Struktur und Pinbelegungsdetails der Geräte:

In den obigen Diagrammen sehen wir, dass jeder der Typen 4 Latches mit einem Ausgang und 2 einzelnen RESET / SET-Eingängen hat. Die Funktion des ENABLE-Pins für alle SET / RESET-Eingänge ist identisch.

Ein logisches HIGH am ENABLE-Pin ermöglicht es den Latch-Zuständen, mit den relevanten Ausgängen verbunden zu werden. Ein logisches Low oder 0 trennt die Latch-Zustände von ihren Ausgängen und verursacht einen vollständigen offenen Stromkreis zwischen den Ausgängen.

NOR Latch, NAND Latch Äquivalente Logikdiagramme

Die folgenden Diagramme zeigen die äquivalenten Latches in Form von NOR- und NAND-Latches, die in jedem der 4 Latches der einzelnen ICs vorhanden sind.

Wie wir sehen können, wird jeder der Latch-Blöcke unter Verwendung von 3 logischen Steuereingängen gesteuert, nämlich SET, RESET und ENABLE, daher ist der Ausgang von diesen 3 Eingangszuständen abhängig. Die Wahrheitstabelle für diese 3 logischen Zustände kann aus dem folgenden Diagramm gelernt werden:

In der obigen Wahrheitstabelle kann die Vollform der verschiedenen abgekürzten symbolischen Alphabete wie folgt verstanden werden: S = SET Pin R = RESET Pin E = ENABLE Pin Q = OUTPUT Pin OC = Open Circuit NC = No Change

Die Hauptmerkmale des IC 4043 und des IC 4044 sind nachstehend zusammengefasst:

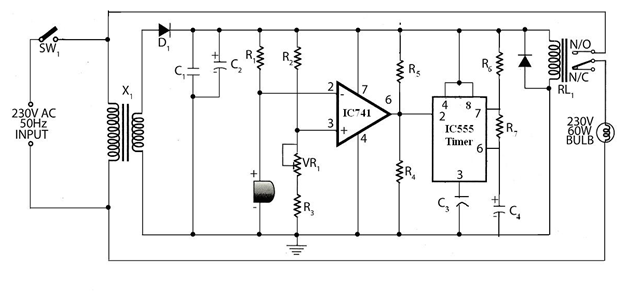

Praktische grundlegende Arbeitssimulation der SET / RESET- und ENABLE-Pins

Arbeitsbeschreibung

Aus dem obigen Simulations-GIF können wir die Funktionsweise der Quad-Latch-Module mit den folgenden Punkten verstehen:

Wenn der SET mit einer positiven Versorgung an einen Pin angelegt wird, geht der Ausgang hoch und wird verriegelt, selbst wenn das positive Potential vom SET-Pin entfernt wird, wie durch die rote LED angezeigt (in Vorwärtsrichtung vorgespannt).

Wenn der RESET-Pin mit einem positiven Impuls angelegt wird, bricht der Latch und der Ausgang geht permanent auf LOW, selbst wenn der positive vom RESET-Pin entfernt wird. Dies wird durch die Beleuchtung der blauen LED angezeigt.

Die obigen Operationen können nur implementiert werden, solange der ENABLE-Pin des IC auf einem positiven Versorgungspotential liegt. Bei Anschluss an ein negatives oder Massepotential wird der Ausgang des Latch offen und reagiert nicht mehr auf die SET / RESET-Operationen.

Zurück: Programmierbare Timer-Schaltung am Wochentag Weiter: Pinbelegung des IC 4033, Datenblatt, Anwendung