Das Feldeffekttransistor (FET) ist ein elektronisches Gerät, in dem ein elektrisches Feld wird verwendet, um den Stromfluss zu regulieren. Um dies zu implementieren, wird eine Potentialdifferenz an die Gate- und Source-Anschlüsse der Vorrichtung angelegt, die die Leitfähigkeit zwischen den Drain- und Source-Anschlüssen ändert, wodurch ein kontrollierter Strom über diese Anschlüsse fließt.

FETs werden aufgerufen unipolare Transistoren weil diese als Einzelträgergeräte ausgelegt sind. Sie finden verschiedene Arten von Feldeffekttransistoren.

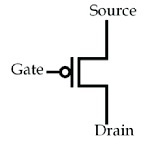

Symbol

Die grafischen Symbole für die n-Kanal- und p-Kanal-JFETs können in den folgenden Abbildungen dargestellt werden.

Sie können deutlich erkennen, dass die Pfeilmarkierungen, die für das n-Kanal-Gerät nach innen zeigen, die Richtung anzeigen, in die ichG(Gate-Strom) soll fließen, wenn der pn-Übergang in Vorwärtsrichtung vorgespannt war.

Bei einem p-Kanal-Gerät sind die Bedingungen bis auf den Richtungsunterschied des Pfeilsymbols identisch.

Unterschied zwischen FET und BJT

Der Feldeffekttransistor (FET) ist ein Gerät mit drei Anschlüssen, das für eine Vielzahl von Schaltungsanwendungen entwickelt wurde, die die des BJT-Transistors in hohem Maße ergänzen.

Während Sie signifikante Abweichungen zwischen BJTs und JFETs feststellen, gibt es tatsächlich mehrere Übereinstimmungsmerkmale, über die in den folgenden Diskussionen gesprochen wird. Der Hauptunterschied zwischen diesen Geräten besteht darin, dass BJT ein stromgesteuertes Gerät ist, wie in Abb. 5.1a dargestellt, während der JFET-Transistor ein spannungsgesteuertes Gerät ist, wie in Abb. 5.1b gezeigt.

Einfach gesagt, der aktuelle I.C.in Abb. 5.1a ist eine unmittelbare Funktion des Niveaus von I.B.. Für den FET ist der Strom I eine Funktion der Spannung V.GSan die Eingangsschaltung gegeben, wie in Abb. 5.1b gezeigt.

In beiden Fällen wird der Strom der Ausgangsschaltung durch einen Parameter der Eingangsschaltung bestimmt. In einer Situation ein Strompegel und in der anderen eine angelegte Spannung.

Genau wie bei npn und pnp für Bipolartransistoren finden Sie n-Kanal- und p-Kanal-Feldeffekttransistoren. Sie sollten sich jedoch daran erinnern, dass der BJT-Transistor ein bipolares Gerät ist. Das Präfix zeigt an, dass der Leitungspegel eine Funktion von zwei Ladungsträgern, Elektronen und Löchern ist.

Der FET hingegen ist a unipolares Gerät Dies hängt ausschließlich von der Elektronenleitung (n-Kanal) oder der Lochleitung (p-Kanal) ab.

Der Ausdruck 'Feldeffekt' kann folgendermaßen erklärt werden: Wir alle sind uns der Fähigkeit eines Permanentmagneten bewusst, Metallspäne ohne physischen Kontakt zum Magneten zu ziehen. In ähnlicher Weise wird innerhalb des FET ein elektrisches Feld durch die vorhandenen Ladungen erzeugt, die den Leitungsweg des Ausgangsschaltkreises beeinflussen, ohne dass ein direkter Kontakt zwischen den steuernden und gesteuerten Größen besteht. Wahrscheinlich eines der wichtigsten Merkmale des FET ist seine hohe Eingangsimpedanz.

Sie reicht von 1 bis zu vielen hundert Megaohm und übertrifft die normalen Eingangswiderstandsbereiche der BJT-Konfigurationen erheblich. Dies ist ein äußerst wichtiges Merkmal bei der Entwicklung linearer Wechselstromverstärkermodelle.

Der BJT ist jedoch empfindlicher gegenüber Änderungen des Eingangssignals. Das heißt, die Änderung des Ausgangsstroms ist bei BJTs üblicherweise signifikant größer als bei FETs bei gleicher Änderung ihrer Eingangsspannungen.

Aus diesem Grund können die Standard-Wechselspannungsverstärkungen für BJT-Verstärker im Vergleich zu FETs viel höher sein.

Im Allgemeinen sind FETs thermisch wesentlich elastischer als BJTs und haben im Vergleich zu BJTs häufig eine kleinere Struktur, wodurch sie speziell für die Einbettung als integrierte Schaltung (I) geeignet sindC)Chips.

Die strukturellen Eigenschaften einiger FETs können es andererseits ermöglichen, dass sie gegenüber physikalischen Kontakten besonders empfindlich sind als BJTs.

Mehr BJT / JFET-Beziehung

- Für einen BJT V.SEIN= 0,7 V ist der wichtige Faktor für den Start einer Analyse seiner Konfiguration.

- Ebenso der Parameter I.G= 0 A ist üblicherweise das erste, was für die Analyse einer JFET-Schaltung berücksichtigt wird.

- Für die BJT-Konfiguration habe ichB.ist oft der erste Faktor, der bestimmt werden muss.

- Ebenso ist es für den JFET typischerweise das V.GS.

In diesem Artikel werden wir uns auf JFETs oder Sperrschicht-Feldeffekttransistoren konzentrieren. Im nächsten Artikel werden wir uns mit Metalloxid-Halbleiter-Feldeffekttransistoren oder MOS-FET befassen.

KONSTRUKTION UND EIGENSCHAFTEN VON JFETs

Wie wir bereits erfahren haben, hat ein JFET 3 Ableitungen. Einer von ihnen steuert den Stromfluss zwischen den beiden anderen.

Genau wie bei BJTs wird auch bei JFETs das n-Kanal-Gerät stärker eingesetzt als die p-Kanal-Gegenstücke, da n-Geräte im Vergleich zum p-Gerät tendenziell effizienter und benutzerfreundlicher sind.

In der folgenden Abbildung sehen wir die Grundstruktur oder den Aufbau eines n-Kanal-JFET. Wir können sehen, dass die Zusammensetzung vom n-Typ den Hauptkanal über die Schichten vom p-Typ bildet.

Der obere Teil des Kanals vom n-Typ ist durch einen ohmschen Kontakt mit einem Anschluss verbunden, der als Drain (D) bezeichnet wird, während der untere Teil desselben Kanals auch über einen ohmschen Kontakt mit einem anderen Anschluss verbunden ist, der als Source (S) bezeichnet wird.

Die paar Materialien vom p-Typ sind zusammen mit dem als Gate (G) bezeichneten Anschluss verbunden. Im Wesentlichen stellen wir fest, dass die Drain- und Source-Anschlüsse mit den Enden des n-Kanals verbunden sind. Der Gate-Anschluss ist mit einem Paar p-Kanal-Material verbunden.

Wenn an einem jfet keine Spannung anliegt, sind seine beiden pn-Übergänge ohne Vorspannungsbedingungen. In dieser Situation existiert an jedem Übergang ein Verarmungsbereich, wie in der obigen Figur gezeigt, der ziemlich wie ein Dioden-pn-Bereich ohne Vorspannung aussieht.

Wasseranalogie

Die Arbeits- und Steueroperationen eines JFET können durch die folgende Wasseranalogie verstanden werden.

Hier kann der Wasserdruck mit der angelegten Spannungsgröße vom Drain zur Source verglichen werden.

Der Wasserfluss kann mit dem Elektronenfluss verglichen werden. Die Öffnung des Hahns ahmt den Quellenanschluss des JFET nach, während der obere Teil des Hahns, in den das Wasser gedrückt wird, den Abfluss des JFET darstellt.

Der Tap-Knopf wirkt wie das Gate des JFET. Mit Hilfe eines Eingangspotentials steuert es den Elektronenfluss (Ladung) vom Drain zur Source, genau wie der Hahnknopf den Wasserfluss an der Mundöffnung steuert.

Aus der JFET-Struktur können wir erkennen, dass sich der Drain- und der Source-Anschluss an den entgegengesetzten Enden des n-Kanals befinden, und da der Begriff auf dem Elektronenfluss basiert, können wir schreiben:

V.GS= 0 V, V.DSEin positiver Wert

In Abb. 5.4 sehen wir eine positive Spannung V.DSüber den n-Kanal angewendet. Der Gate-Anschluss ist direkt mit der Quelle verbunden, um eine Bedingung V zu erzeugenGS= 0V. Dies ermöglicht, dass das Gate und die Source-Anschlüsse auf einem identischen Potential liegen, und führt zu einem Verarmungsbereich am unteren Ende jedes p-Materials, genau wie wir es im ersten Diagramm oben mit einer Bedingung ohne Vorspannung sehen.

Sobald eine Spannung V vorliegtDD(= V.DS) angelegt werden, werden Elektronen zum Drain-Anschluss gezogen, wodurch der herkömmliche Stromfluss ID erzeugt wird, wie in Abb. 5.4 gezeigt.

Die Richtung des Ladungsflusses zeigt, dass der Drain- und der Source-Strom gleich groß sind (I.D.= IchS.). Gemäß den in Abb. 5.4 dargestellten Bedingungen wirkt der Ladungsfluss recht uneingeschränkt und wird nur durch den Widerstand des n-Kanals zwischen Drain und Source beeinflusst.

Sie können beobachten, dass der Verarmungsbereich um den oberen Abschnitt beider p-Typ-Materialien größer ist. Dieser Größenunterschied der Region wird idealerweise durch Abb. 5.5 erklärt. Stellen wir uns einen gleichmäßigen Widerstand im n-Kanal vor, der in die in Abb. 5.5 angegebenen Abschnitte aufgeteilt werden könnte.

Das aktuelle I.D.kann die Spannungsbereiche durch den Kanal aufbauen, wie in der gleichen Abbildung gezeigt. Infolgedessen wird der obere Bereich des Materials vom p-Typ um einen Pegel von etwa 1,5 V in Sperrrichtung vorgespannt, wobei der untere Bereich lediglich um 0,5 V in Sperrrichtung vorgespannt wird.

Der Punkt, an dem der pn-Übergang entlang des gesamten Kanals in Sperrrichtung vorgespannt ist, führt zu einem Gate-Strom mit null Ampere, wie in derselben Figur dargestellt. Diese Eigenschaft, die zu I führtG= 0 A ist ein wichtiges Merkmal des JFET.

Als V.DSDas Potential wird von 0 auf einige Volt erhöht, der Strom steigt gemäß dem Ohmschen Gesetz und der Darstellung von I.D.Zeile 5DSkann wie in Abb. 5.6 gezeigt aussehen.

Die vergleichende Geradheit des Diagramms zeigt, dass für die Bereiche mit niedrigem Wert von V.DSist der Widerstand grundsätzlich gleichmäßig. Als V.DSsteigt und nähert sich einem in Abb. 5.6 als VP bekannten Wert, erweitern sich die Verarmungsbereiche wie in Abb. 5.4 angegeben.

Dies führt zu einer offensichtlichen Verringerung der Kanalbreite. Der verringerte Leitungsweg führt zu einer Erhöhung des Widerstands, wodurch die Kurve von Abb. 5.6 entsteht.

Je horizontaler die Kurve wird, desto höher ist der Widerstand, was darauf hinweist, dass der Widerstand im horizontalen Bereich in Richtung „unendlicher“ Ohm geht. Wenn V.DSsteigt in einem Ausmaß an, in dem es den Anschein hat, als könnten sich die beiden Verarmungsbereiche „berühren“, wie in Abb. 5.7 dargestellt, was zu einer Situation führt, die als Quetschen bekannt ist.

Der Betrag, um den V.DSentwickelt diese Situation heißt die abknipsen Spannung und es wird durch V symbolisiertP.wie in Abb. 5.6 dargestellt. Im Allgemeinen ist das Wort 'Pinch-Off' irreführend, da es den Strom I impliziertD.wird 'eingeklemmt' und fällt auf 0 A. Wie in Abb. 5.6 gezeigt, ist dies in diesem Fall kaum ersichtlich. ichD.behält einen Sättigungsgrad bei, der als I charakterisiert istDSSin Abb. 5.6.

Die Wahrheit ist, dass es weiterhin einen sehr kleinen Kanal mit einem Strom von signifikant hoher Konzentration gibt.

Der Punkt, an dem die ID nicht abfällt abknipsen und bewahrt den in Abb. 5.6 angegebenen Sättigungsgrad, der mit folgendem Beweis bestätigt wird:

Da es keinen Drainstrom gibt, wird die Möglichkeit unterschiedlicher Potentialpegel durch das n-Kanal-Material zur Bestimmung der sich ändernden Beträge der Sperrvorspannung entlang des pn-Übergangs ausgeschlossen. Das Endergebnis ist der Verlust der ausgelösten Verarmungsbereichsverteilung abknipsen beginnen mit.

Wenn wir V erhöhenDSüber V.P.Der Bereich mit engem Kontakt, in dem die beiden Verarmungsbereiche aufeinander treffen, nimmt entlang des Kanals an Länge zu. Die ID-Ebene bleibt jedoch im Wesentlichen unverändert.

So ist der Moment V.DSist höher als V.pDer JFET erfasst die Eigenschaften der Stromquelle.

Wie in Abb. 5.8 gezeigt, wird der Strom in einem JFET bei I bestimmtD.= IchDSS, aber Spannung V.DShöher als VP wird durch die angeschlossene Last hergestellt.

Die Auswahl der IDSS-Notation basiert auf der Tatsache, dass es sich um den Strom Drain to Source handelt, der eine kurzgeschlossene Verbindung zwischen Gate und Source aufweist.

Weitere Untersuchungen ergeben folgende Bewertung:

ichDSSist der höchste Drainstrom für einen JFET und wird durch die Bedingungen V festgelegtGS= 0 V und V.DS> | VP |.

Beachten Sie, dass in Abb. 5.6 V.GSist 0 V für die gesamte Strecke der Kurve. In den folgenden Abschnitten erfahren Sie, wie die Attribute in Abb. 5.6 als Pegel von V beeinflusst werdenGSist vielfältig.

V.GS <0V

Die an Gate und Source angelegte Spannung wird als VGS bezeichnet, die für die Steuerung der JFET-Operationen verantwortlich ist.

Nehmen wir das Beispiel eines BJT, genau wie die Kurven von I.C.vs V.DIESwerden für verschiedene Niveaus von I bestimmtB.ähnlich die Kurven von I.D.vs V.DSfür verschiedene Niveaus von V.GSkann für ein JFET-Gegenstück erstellt werden.

Hierzu wird der Gate-Anschluss auf ein weiter niedrigeres Potential unterhalb des Pegels des Source-Potentials eingestellt.

Bezugnehmend auf die folgende Abbildung 5.9 wird für ein reduziertes V eine -1V an die Gate- / Source-Anschlüsse angelegtDSNiveau.

Das Ziel der negativen Potentialvorspannung V.GSist es, Verarmungsregionen zu entwickeln, die der Situation von V ähnelnGS= 0, aber bei signifikant reduziertem V.DS.

Dies bewirkt, dass das Gate einen Sättigungspunkt mit einem niedrigeren Pegel von V erreichtDSwie in Abb. 5.10 angegeben (V.GS= -1V).

Der entsprechende Sättigungspegel für I.D.kann als reduziert befunden werden und nimmt tatsächlich einfach weiter ab als V.GSwird negativer gemacht.

In Abb. 5.10 sehen Sie deutlich, wie die Quetschspannung mit einer parabolischen Form wie V weiter abfälltGSwird immer negativer.

Schließlich, wenn V.GS= -Vpwird es ausreichend negativ, um einen Sättigungspegel herzustellen, der schließlich 0 mA beträgt. Auf dieser Ebene ist der JFET vollständig ausgeschaltet.

Das Niveau von V.GSwas mich verursachtD.0 mA zu erreichen ist gekennzeichnet durch V.GS= V.P.worin V.P.ist eine negative Spannung für n-Kanal-Bauelemente und eine positive Spannung für p-Kanal-JFETs.

In der Regel werden die meisten JFET-Datenblätter angezeigt abknipsen Spannung angegeben als V.GS (aus)anstelle von V.P..

Der Bereich auf der rechten Seite des Pinch-Off-Locus in der obigen Abbildung ist der Ort, der herkömmlicherweise in linearen Verstärkern verwendet wird, um ein verzerrungsfreies Signal zu erzielen. Diese Region wird allgemein genannt Konstantstrom-, Sättigungs- oder linearer Verstärkungsbereich.

Spannungsgesteuerter Widerstand

Der Bereich, der sich in derselben Figur auf der linken Seite des Quetschpunkts befindet, wird als bezeichnet Ohmscher Bereich oder der spannungsgesteuerte Widerstandsbereich.

In diesem Bereich kann das Gerät tatsächlich als variabler Widerstand betrieben werden (zum Beispiel bei automatischen Verstärkungsregelungsanwendungen), wobei sein Widerstand über das angelegte Gate / Source-Potential gesteuert wird.

Sie können sehen, dass die Steigung jeder der Kurven auch den Drain / Source-Widerstand des JFET für V anzeigtDS

Wenn wir VGS mit negativem Potential erhöhen, wird die Steigung jeder Kurve immer horizontaler und zeigt proportional ansteigende Widerstandsniveaus.

Durch die folgende Gleichung können wir eine gute anfängliche Annäherung an das Niveau des Widerstands in Bezug auf die VGS-Spannung erhalten.

p-Kanal JFET funktioniert

Das interne Layout und der Aufbau eines p-Kanal-JFET sind genau identisch mit dem n-Kanal-Gegenstück, außer dass die Materialbereiche vom p- und n-Typ umgekehrt sind, wie unten gezeigt:

Die Richtungen des Stromflusses können zusammen mit den tatsächlichen Polaritäten der Spannung VGS und VDS auch als umgekehrt angesehen werden. Im Fall eines p-Kanal-JFET wird der Kanal als Reaktion auf ein zunehmendes positives Potential über dem Gate / der Source eingeschränkt.

Die Notation mit einem doppelten Index für die V.DSführt zu einer negativen Spannung für V.DS, wie in den Eigenschaften von Abb.5.12 gezeigt. Hier findest du michDSSbei 6 mA, während eine Quetschspannung bei V.GS= + 6V.

Bitte lassen Sie sich nicht verwirren, da Sie ein Minuszeichen für das V habenDS. Es zeigt lediglich an, dass die Quelle ein höheres Potential als der Drain trägt.

Sie können sehen, dass die Kurven für hohe V.DSDie Pegel steigen abrupt auf Werte an, die uneingeschränkt wirken. Der angezeigte Anstieg, der vertikal ist, symbolisiert eine Durchschlagsituation, was bedeutet, dass der Strom durch das Kanalgerät zu diesem Zeitpunkt vollständig von der externen Schaltung gesteuert wird.

Obwohl dies in Abb. 5.10 für n-Kanal-Geräte nicht ersichtlich ist, kann dies unter ausreichend hoher Spannung möglich sein.

Dieser Bereich kann beseitigt werden, wenn der V.DS (max)wird aus dem Datenblatt des Geräts notiert, und das Gerät ist so konfiguriert, dass das tatsächliche V.DSWert ist niedriger als dieser notierte Wert für jedes V.GS.

Zurück: 5 besten 40-Watt-Verstärkerschaltungen untersucht Weiter: 2N3055 Datenblatt, Pinbelegung, Anwendungsschaltungen