Für die Ausführung eines Computerprogramms ist das synchrone Arbeiten von mehr als einer Komponente eines Computers erforderlich. Beispielsweise, Prozessoren - Bereitstellung der erforderlichen Steuerinformationen, Adressen usw. usw., Busse - Übertragung von Informationen und Daten zum und vom Speicher zu E / A-Geräten usw. Der interessante Faktor des Systems wäre die Art und Weise, wie es die Übertragung von Informationen zwischen Prozessor-, Speicher- und E / A-Geräten handhabt. Normalerweise steuern Prozessoren den gesamten Prozess der Datenübertragung, von der Einleitung der Übertragung bis zur Speicherung der Daten am Zielort. Dies erhöht die Belastung des Prozessors und bleibt die meiste Zeit im Idealzustand, wodurch die Effizienz des Systems verringert wird. Um die Datenübertragung zwischen E / A-Geräten und Speicher zu beschleunigen, fungiert der DMA-Controller als Stationsmaster. Der DMA-Controller überträgt Daten mit minimalem Eingriff des Prozessors.

Was ist ein DMA-Controller?

Der Begriff DMA steht für direkten Speicherzugriff. Das für den direkten Speicherzugriff verwendete Hardwaregerät wird als DMA-Controller bezeichnet. DMA Controller ist eine Steuereinheit , Teil von E / A-Geräten Schnittstellenschaltung , die Datenblöcke zwischen E / A-Geräten und Hauptspeicher mit minimalem Eingriff des Prozessors übertragen können.

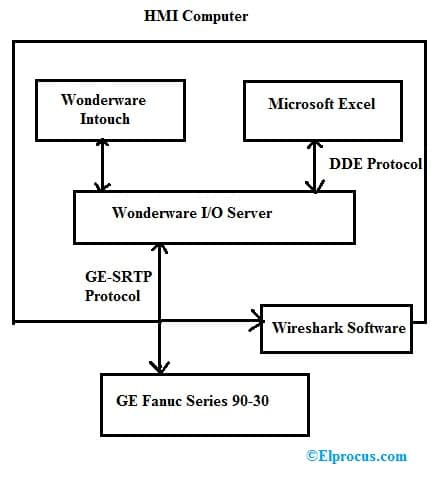

DMA-Controller-Diagramm in der Computerarchitektur

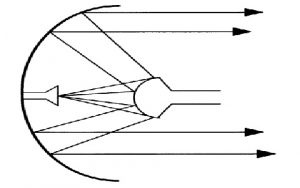

Der DMA-Controller bietet eine Schnittstelle zwischen dem Bus und den Ein- / Ausgabegeräten. Obwohl es Daten ohne Eingreifen des Prozessors überträgt, wird es vom Prozessor gesteuert. Der Prozessor initiiert den DMA-Controller durch Senden der Startadresse, der Anzahl der Wörter im Datenblock und der Richtung der Datenübertragung .i.e. vom E / A-Gerät zum Speicher oder vom Hauptspeicher zum E / A-Gerät. Es kann mehr als ein externes Gerät an den DMA-Controller angeschlossen werden.

DMA in Computerarchitektur

Der DMA-Controller enthält eine Adresseinheit zum Generieren von Adressen und zum Auswählen des E / A-Geräts für die Übertragung. Es enthält auch die Steuereinheit und die Datenanzahl, um die Anzahl der übertragenen Blöcke zu zählen und die Richtung der Datenübertragung anzugeben. Wenn die Übertragung abgeschlossen ist, informiert DMA den Prozessor durch Auslösen eines Interrupts. Das typische Blockdiagramm des DMA-Controllers ist in der folgenden Abbildung dargestellt.

Typisches Blockdiagramm eines DMA-Controllers

Arbeitsweise des DMA Controllers

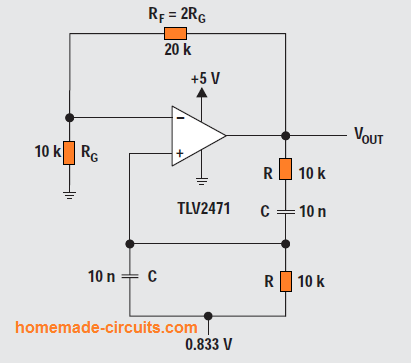

Der DMA-Controller muss den Bus mit dem Prozessor teilen, um die Datenübertragung durchzuführen. Das Gerät, das den Bus zu einem bestimmten Zeitpunkt hält, wird als Busmaster bezeichnet. Wenn eine Übertragung vom E / A-Gerät in den Speicher oder umgekehrt erfolgen muss, stoppt der Prozessor die Ausführung des aktuellen Programms schrittweise das Programm Zähler, verschiebt Daten über den Stapel und sendet dann ein DMA-Auswahlsignal über den Adressbus an den DMA-Controller.

Wenn der DMA-Controller frei ist, fordert er die Steuerung des Busses vom Prozessor an, indem er das Busanforderungssignal erhöht. Der Prozessor gewährt dem Controller den Bus durch Erhöhen des Busgewährungssignals. Jetzt ist der DMA-Controller der Busmaster. Der Prozessor initiiert den DMA-Controller durch Senden der Speicheradressen, der Anzahl der zu übertragenden Datenblöcke und der Richtung der Datenübertragung. Nachdem die Datenübertragungsaufgabe dem DMA-Controller zugewiesen wurde, setzt der Prozessor die Ausführung des Programms fort, nachdem er Anweisungen vom Stapel abgerufen hat, anstatt idealerweise bis zum Abschluss der Datenübertragung zu warten.

Datenübertragung im Computer durch DMA-Controller

Der DMA-Controller hat jetzt die volle Kontrolle über Busse und kann unabhängig von der CPU direkt mit Speicher- und E / A-Geräten interagieren. Die Datenübertragung erfolgt gemäß den vom Prozessor empfangenen Steueranweisungen. Nach Abschluss der Datenübertragung wird das Busanforderungssignal deaktiviert, und die CPU deaktiviert das Busgewährungssignal, wodurch die Steuerung der Busse zur CPU verschoben wird.

Wenn ein E / A-Gerät die Übertragung initiieren möchte, sendet es ein DMA-Anforderungssignal an den DMA-Controller, für das der Controller bestätigt, ob es frei ist. Dann fordert die Steuerung den Prozessor nach dem Bus an und erhöht das Busanforderungssignal. Nach dem Empfang des Busbewilligungssignals werden die Daten vom Gerät übertragen. Für einen n-kanalisierten DMA-Controller können n externe Geräte angeschlossen werden.

Der DMA überträgt die Daten in drei Modi, darunter die folgenden.

zu) Burst-Modus : In diesem Modus übergibt DMA die Busse erst nach Abschluss der gesamten Datenübertragung an die CPU. Wenn die CPU den Bus benötigt, muss sie ideal bleiben und auf die Datenübertragung warten.

b) Cycle Stealing-Modus : In diesem Modus steuert DMA die Busse nach der Übertragung jedes Bytes an die CPU. Es gibt kontinuierlich eine Anforderung zur Bussteuerung aus, überträgt ein Byte und gibt den Bus zurück. Dadurch muss die CPU nicht lange warten, wenn sie einen Bus für Aufgaben mit höherer Priorität benötigt.

c) Transparenter Modus: Hier überträgt DMA Daten nur, wenn die CPU den Befehl ausführt, für den keine Busse erforderlich sind.

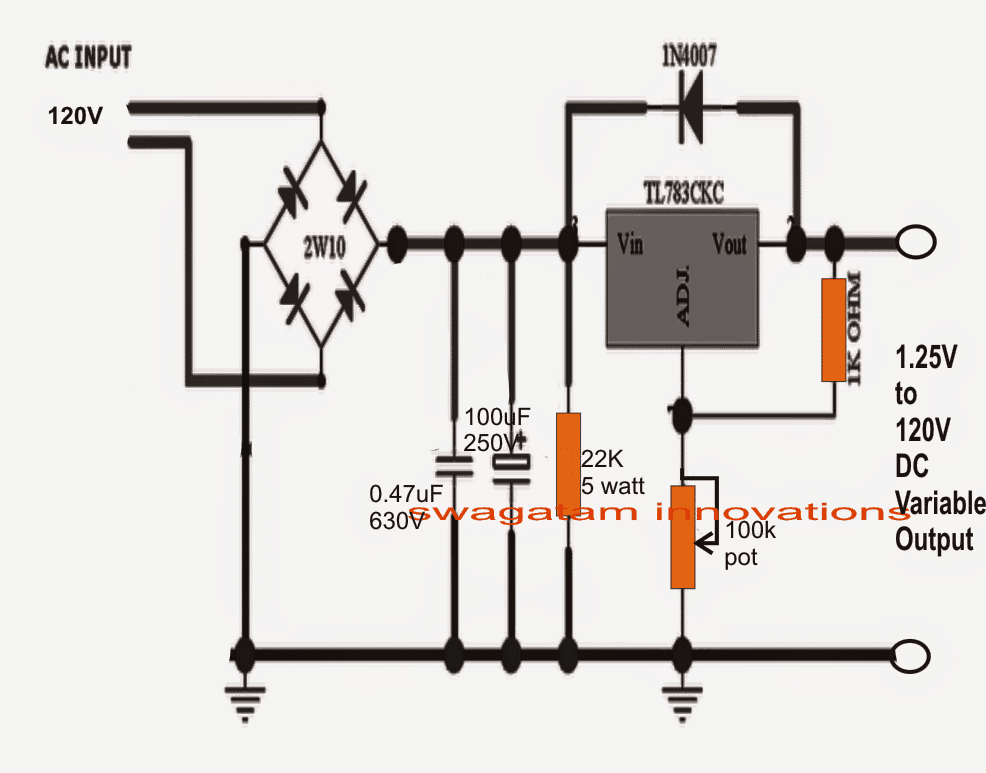

8237 DMA-Controller

- 8237 verfügt über 4 E / A-Kanäle sowie die Flexibilität, die Anzahl der Kanäle zu erhöhen.

- Jeder Kanal kann einzeln programmiert werden und verfügt über eine 64k-Adresse und Datenfähigkeit.

- Der Zeitsteuerungsblock, der Programmbefehlssteuerblock und der Prioritätscodiererblock sind die drei Hauptblöcke von 8237A.

- Die internen Zeitsteuerungs- und externen Steuersignale werden vom Zeitsteuerungsblock angesteuert.

- Verschiedene Befehle, die der Mikroprozessor dem DMA gibt, werden vom Programmbefehlssteuerblock decodiert.

- Welcher Kanal die höchste Priorität erhalten muss, hängt von der Priorität ab Geberblock .

8237A hat 27 interne Register.

8237A arbeitet in zwei Zyklen - Idealer Zyklus und aktiver Zyklus, wobei jeder Zyklus 7 separate Zustände enthält, die jeweils aus einer Taktperiode bestehen.

S0 - Der erste Zustand, in dem die Steuerung den Bus angefordert und auf die Bestätigung vom Prozessor gewartet hat.

S1, S2, S3, S4 werden als Arbeitszustände des 8237A bezeichnet, in denen die eigentliche Datenübertragung stattfindet. Wenn mehr Zeit für die Übertragung benötigt wird, werden Wartezustände zwischen diesen Zuständen hinzugefügt.

Für die Speicher-zu-Speicher-Übertragung müssen Lese-aus-Speicher- und Schreib-in-Speicher-Übertragungen durchgeführt werden. Für eine einzelne Übertragung sind acht Zustände erforderlich. Die ersten vier Zustände mit den Indizes S11, S12, S13, S14 führen die Übertragung aus dem Speicher durch, und die nächsten vier Zustände S21, S22, S23, S24 sind für die Übertragung in den Speicher vorgesehen.

DMA geht in den idealen Zustand über, wenn kein Kanal einen Dienst anfordert, und führt den SI-Zustand aus. SI ist ein inaktiver Zustand, in dem der DMA inaktiv ist, bis er eine Anforderung empfängt. In diesem Zustand befindet sich DMA in einem Programmzustand, in dem der Prozessor den DMA programmieren kann.

Wenn sich DMA im Idealzustand befindet und keine weiteren Kanalanforderungen erhält, gibt es ein HRQ-Signal an den Prozessor aus und wechselt in den aktiven Zustand, in dem die Datenübertragung entweder im Burst-Modus, im Zyklus-Stealing-Modus oder im transparenten Modus gestartet werden kann.

8237 Pin-Diagramm

8257 DMA-Controller

In Verbindung mit einem einzelnen Intel 8212 I / O-Port-Gerät bildet der 8257 DMA-Controller einen vollständigen 4-Kanal DMA-Controller . Nach Erhalt einer Übertragungsanforderung wird der 8257 Controller-

- Übernimmt die Steuerung über den Systembus vom Prozessor.

- Das mit dem Kanal mit der höchsten Priorität verbundene Peripheriegerät wird bestätigt.

- Die niedrigstwertigen Bits der Speicheradresse werden über die Adressleitungen A0-A7 des Systembusses verschoben.

- Das bedeutendste 8 Bits der Speicheradresse werden über Datenleitungen zum 8212-E / A-Port geführt.

- Erzeugt die entsprechenden Steuersignale für die Datenübertragung zwischen Peripheriegeräten und adressierten Speicherplätzen.

- Wenn die angegebene Anzahl von Bytes übertragen wird, informiert der Controller das CPU-Ende der Übertragung durch Aktivieren des TC-Ausgangs (Terminal Count).

Für jeden Kanal enthält 8257 zwei 16-Bit-Register - 1) DMA-Adressregister und 2) Terminalzählregister, das initialisiert werden sollte, bevor ein Kanal aktiviert wird. Die Adresse des ersten Speicherplatzes, auf den zugegriffen werden soll, wird in das DMA-Adressregister geladen. Die niederwertigen 14 Bits des in das Terminalzählregister geladenen Werts geben die Anzahl der DMA-Zyklen minus eins vor der Aktivierung des Terminalzählausgangs an. Die Art der Operation für einen Kanal wird durch die höchstwertigen zwei Bits des Terminalzählregisters angezeigt.

8257 Pin-Diagramm

Vor- und Nachteile des DMA-Controllers

Die Vor- und Nachteile des DMA-Controllers umfassen Folgendes.

Vorteile

- DMA beschleunigt die Speicheroperationen, indem die Beteiligung der CPU umgangen wird.

- Die Arbeitsüberlastung der CPU nimmt ab.

- Für jede Übertragung sind nur wenige Taktzyklen erforderlich

Nachteile

- Ein Cache-Kohärenzproblem kann gesehen werden, wenn DMA für die Datenübertragung verwendet wird.

- Erhöht den Preis des Systems.

DMA ( Direkter Speicherzugriff ) Controller wird in Grafikkarten, Netzwerkkarten, Soundkarten usw. verwendet. DMA wird auch für die Übertragung innerhalb eines Chips in Mehrkernprozessoren verwendet. DMA arbeitet in einem seiner drei Modi und kann die Prozessorlast erheblich reduzieren. In welchen DMA-Modi haben Sie gearbeitet? Welcher der von Ihnen betrachteten Modi ist effektiver?