Eine Pufferstufe ist im Grunde eine verstärkte Zwischenstufe, die es dem Eingangsstrom ermöglicht, den Ausgang zu erreichen, ohne von der Ausgangsbelastung beeinflusst zu werden.

In diesem Beitrag werden wir versuchen zu verstehen, was digitale Puffer sind, und wir werden einen Blick auf deren Definition, Symbol, Wahrheitstabelle, doppelte Inversion unter Verwendung des logischen 'NICHT' -Gatters, digitaler Puffer, Fan-Out-Fan-In, Tri-State-Puffer, werfen. Drei-Zustands-Puffer-Schalteräquivalent, Aktiver 'HIGH' Drei-Zustands-Puffer, Aktiver 'HIGH' invertierender Drei-Zustands-Puffer, Aktiver 'LOW' -Zustands-Drei-Zustands-Puffer, Aktiver 'LOW' -Invertierungs-Drei-Zustands-Puffer, Drei-Zustands-Puffersteuerung , Tri-State-Buffer-Datenbus-Steuerung und schließlich werden wir einen Überblick über allgemein verfügbare digitale Puffer- und Tri-State-Buffer-ICs geben.

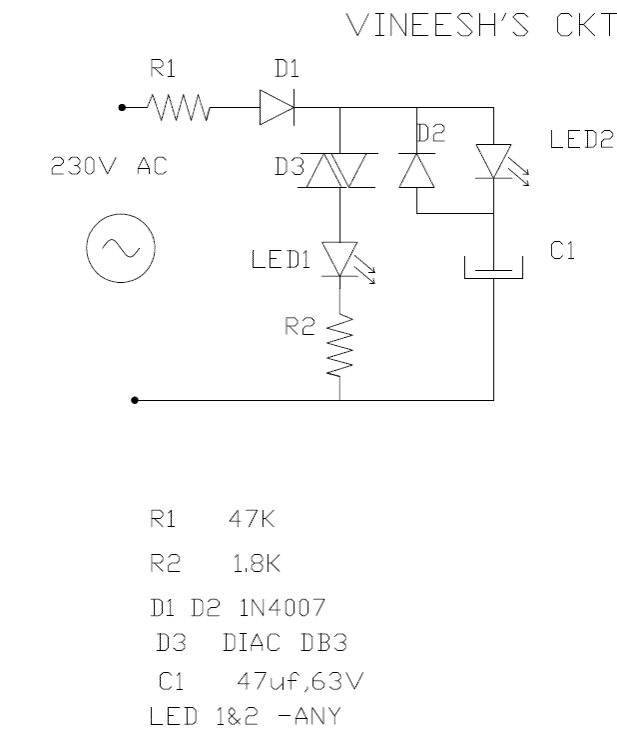

In einem der vorherigen Beiträge haben wir etwas über das logische „NICHT“ -Gatter gelernt, das auch als digitaler Wechselrichter bezeichnet wird. In einem NICHT-Gatter ist der Ausgang immer komplementär zum Eingang.

Wenn der Eingang also 'HIGH' ist, wird der Ausgang 'LOW', wenn der Eingang 'LOW' ist, wird der Ausgang 'HIGH', so dass dies als Wechselrichter bezeichnet wird.

Es kann vorkommen, dass der Ausgang vom Eingang getrennt oder isoliert werden muss oder dass der Eingang sehr schwach ist und Lasten ansteuern muss, die einen höheren Strom benötigen, ohne die Polarität des Signals mithilfe eines Relais oder eines Transistors usw. umzukehren. In solchen Situationen werden digitale Puffer nützlich und werden effektiv als Puffer zwischen der Signalquelle und der tatsächlichen Lasttreiberstufe angewendet.

Eine solche Logikgatter Dieser Signalausgang wird als digitaler Puffer bezeichnet.

Ein digitaler Puffer führt keine Inversion des eingespeisten Signals durch und ist auch kein 'Entscheidungsfindungsgerät' wie das logische 'NICHT' -Gatter, sondern gibt den gleichen Ausgang wie der Eingang aus.

Illustration des digitalen Puffers:

Das obige Symbol ähnelt dem logischen 'NICHT' -Gatter ohne das 'o' an der Spitze des Dreiecks, was bedeutet, dass keine Inversion durchgeführt wird.

Die Boolesche Gleichung für den digitalen Puffer lautet Y = A.

'Y' ist der Eingang und 'A' Ausgang.

Wahrheitstabelle:

Doppelte Inversion mit logischen 'NICHT' -Gattern:

Ein digitaler Puffer kann unter Verwendung von zwei logischen 'NICHT' -Gattern auf folgende Weise aufgebaut werden:

Das Eingangssignal wird zuerst durch das erste NICHT-Gatter auf der linken Seite invertiert, und das invertierte Signal wird dann durch das nächste 'NICHT' -Gatter auf der rechten Seite weiter invertiert, wodurch der Ausgang dem Eingang entspricht.

Warum digitale Puffer verwendet werden

Jetzt kratzen Sie sich vielleicht am Kopf, warum der digitale Puffer überhaupt existiert. Er funktioniert nicht wie andere Logikgatter. Wir könnten den digitalen Puffer einfach aus einer Schaltung werfen und ein Stück Draht anschließen. Richtig? Nicht wirklich.

Hier ist die Antwort : Ein Logikgatter benötigt keinen hohen Strom, um Operationen auszuführen. Es ist nur ein Spannungspegel (5V oder 0V) bei niedrigem Strom ausreichend.

Alle Arten von Logikgattern unterstützen hauptsächlich einen eingebauten Verstärker, so dass der Ausgang nicht von Eingangssignalen abhängig ist. Wenn wir zwei logische 'NICHT' -Gatter in Reihe kaskadieren, erhalten wir die gleiche Signalpolarität wie der Eingang am Ausgangspin, jedoch mit relativ höherem Strom. Mit anderen Worten, der digitale Puffer funktioniert wie ein digitaler Verstärker.

Ein digitaler Puffer kann als Isolationsstufe zwischen Signalgeneratorstufen und Treiberstufen verwendet werden und hilft auch zu verhindern, dass die Impedanz eine Schaltung von einer anderen beeinflusst.

Ein digitaler Puffer kann eine höhere Stromkapazität bereitstellen, die zum effizienteren Ansteuern von Schalttransistoren verwendet werden kann.

Der digitale Puffer bietet eine höhere Verstärkung, die auch als 'Fan-Out' -Funktion bezeichnet wird.

Fan-Out-Funktion für digitale Puffer:

AUSSCHWÄRMEN : Das Fan-Out kann als die Anzahl der Logikgatter oder digitalen ICs definiert werden, die von einem digitalen Puffer (oder beliebigen digitalen ICs) parallel angesteuert werden können.

Ein typischer digitaler Puffer hat einen Fan-Out von 10, was bedeutet, dass der digitale Puffer 10 digitale ICs parallel ansteuern kann.

FAN-IN : Der Fan-In ist die Anzahl der digitalen Eingänge, die vom digitalen Logikgatter oder vom digitalen IC akzeptiert werden können.

In dem obigen Schema hat der digitale Puffer einen Fan-In von 1, was einen Eingang bedeutet. Ein logisches UND-Gatter mit zwei Eingängen hat einen Fan-In von zwei und so weiter.

Aus dem obigen Schema ist ein Puffer mit den 3 Eingängen von drei verschiedenen Logikgattern verbunden.

Wenn wir nur ein Stück Draht anstelle des Puffers in der obigen Schaltung anschließen, ist das Eingangssignal möglicherweise nicht ausreichend mit Strom versorgt und führt dazu, dass die Spannung über den Gates abfällt und das Signal möglicherweise nicht einmal erkennt.

Zusammenfassend wird also ein digitaler Puffer zum Verstärken eines digitalen Signals mit höherem Stromausgang verwendet.

Tri-State-Puffer

Jetzt wissen wir, was ein digitaler Puffer tut und warum er in elektronischen Schaltkreisen vorhanden ist. Diese Puffer haben zwei Zustände 'HIGH' und 'LOW'. Es gibt einen anderen Puffertyp, der als 'Tri-State-Puffer' bezeichnet wird.

Dieser Puffer verfügt über einen zusätzlichen Pin namens 'Enable Pin'. Mit dem Freigabepin können wir den Ausgang elektronisch vom Eingang verbinden oder trennen.

Wie ein normaler Puffer arbeitet er als digitaler Verstärker und gibt das gleiche Ausgangssignal wie das Eingangssignal. Der einzige Unterschied besteht darin, dass der Ausgang über den Freigabepin elektronisch verbunden und getrennt werden kann.

Es wird also ein dritter Zustand eingeführt, bei dem der Ausgang weder 'HOCH' noch 'NIEDRIG' ist, sondern ein Leerlaufzustand oder eine hohe Impedanz am Ausgang und nicht auf die Eingangssignale reagiert. Dieser Zustand wird als 'HIGH-Z' oder 'HI-Z' bezeichnet.

Das Obige ist das Ersatzschaltbild des Drei-Zustands-Puffers. Der Aktivierungsstift kann den Ausgang vom Eingang verbinden oder trennen.

Es gibt vier Arten von Tri-State-Puffern:

• Aktiver Tri-State-Puffer „HIGH“

• Aktiver Tri-State-Puffer „LOW“

• Aktiver 'HIGH' Invertierender Tri-State-Puffer

• Aktiver “LOW” Invertierender Tri-State-Puffer

Schauen wir uns jeden nacheinander an.

Aktiver Drei-Zustands-Puffer „HIGH“

Im aktiven Drei-Zustands-Puffer „HIGH“ (zum Beispiel: 74LS241) wird der Ausgangspin mit dem Eingangspin verbunden, wenn am Freigabepin „HIGH“ oder „1“ oder ein positives Signal angelegt wird.

Wenn wir 'LOW' oder '0' oder ein negatives Signal an den Freigabepin anlegen, wird der Ausgang vom Eingang getrennt und geht in den Zustand 'HI-Z', in dem der Ausgang nicht auf den Eingang reagiert und der Ausgang im Leerlauf ist.

Aktiver Drei-Zustands-Puffer „LOW“

Hier wird der Ausgang mit dem Eingang verbunden, wenn wir am Freigabepin „LOW“ oder „0“ oder ein negatives Signal anlegen.

Wenn wir 'HIGH' oder '1' oder ein positives Signal anlegen, um den Pin zu aktivieren, wird der Ausgang vom Eingang getrennt und der Ausgang befindet sich im Zustand 'HI-Z' / Leerlauf.

Wahrheitstabelle:

Aktiver 'HIGH' invertierender Tri-State-Puffer

Im aktiven invertierenden Tri-State-Puffer „HIGH“ (Beispiel: 74LS240) fungiert das Gate als logisches „NOT“ -Gatter, jedoch mit dem Freigabepin.

Wenn wir am Freigabeeingang „HIGH“ oder „1“ oder ein positives Signal anlegen, wird das Gate aktiviert und verhält sich wie ein reguläres logisches „NOT“ -Gatter, dessen Ausgang invertiert / komplementär zum Eingang ist.

Wenn wir den Freigabepin mit „LOW“ oder „0“ oder einem negativen Signal versorgen, befindet sich der Ausgang im Zustand „HI-Z“ oder im Leerlauf.

Wahrheitstabelle:

Aktiver 'LOW' Invertierender Tri-State-Puffer:

Im aktiven 'LOW' -Invertierungs-Tri-State-Puffer fungiert das Gate als logisches 'NOT' -Gatter, jedoch mit Freigabepin.

Wenn wir 'LOW' oder '0' oder ein negatives Signal anlegen, um den Pin zu aktivieren, wird das Gate aktiviert und funktioniert wie ein normales logisches 'NOT' -Gatter.

Wenn wir zum Aktivieren des Pins „HIGH“ oder „1“ oder ein positives Signal anlegen, befindet sich der Ausgangspin im Zustand „HI-Z“ / im Leerlaufzustand.

Wahrheitstabelle:

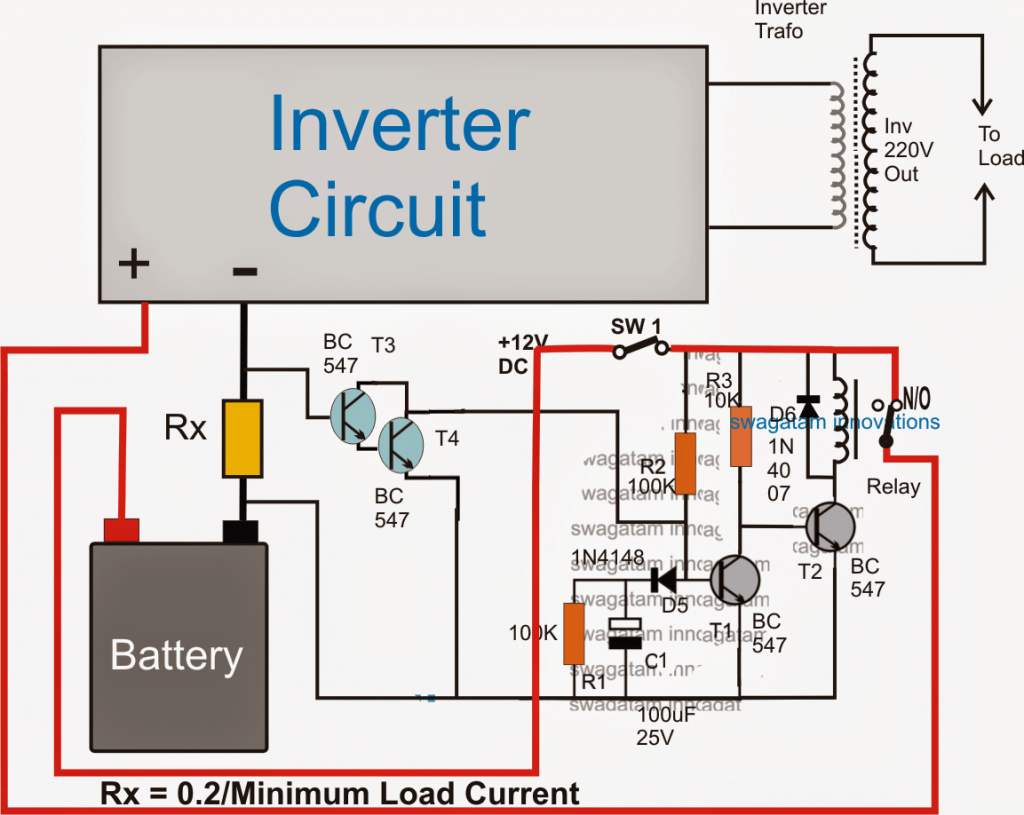

Tri-State-Puffersteuerung:

Aus dem Obigen haben wir gesehen, dass ein Puffer eine digitale Verstärkung bereitstellen kann und Drei-Zustands-Puffer seinen Ausgang vollständig vom Eingang trennen und einen Leerlaufzustand ergeben können.

In diesem Abschnitt erfahren Sie mehr über die Anwendung des Drei-Zustands-Puffers und dessen Verwendung in digitalen Schaltkreisen zur effizienten Verwaltung der Datenkommunikation.

In digitalen Schaltkreisen finden wir einen Datenbus / Drähte, die Daten transportieren. Sie transportieren alle Arten von Daten in einem einzigen Bus, um die Überlastung der Drähte zu verringern / Leiterplattenspuren zu reduzieren und auch die Herstellungskosten zu senken.

An jedem Ende des Busses sind mehrere Logikbausteine, Mikroprozessoren und Mikrocontroller verbunden, die versuchen, gleichzeitig miteinander zu kommunizieren, was zu einem sogenannten Konflikt führt.

In einem Stromkreis treten Konflikte auf, wenn einige Geräte in einem Bus gleichzeitig 'HOCH' und einige Geräte 'NIEDRIG' fahren, was einen Kurzschluss und Schäden in einem Stromkreis verursacht.

Der Tri-State-Puffer kann solche Konflikte vermeiden und Daten ordnungsgemäß über einen Bus senden und empfangen.

Der Drei-Zustands-Puffer wird verwendet, um Logikbausteine, Mikroprozessoren und Mikrocontroller in einem Datenbus voneinander zu isolieren. Ein Decoder erlaubt nur einem Satz von Drei-Zustands-Puffern, Daten durch den Bus zu leiten.

Angenommen, der Datensatz „A“ ist mit einem Mikrocontroller verbunden, der Datensatz „B“ mit einem Mikroprozessor und der Datensatz „C“ mit einigen Logikschaltungen.

In dem obigen Schema sind alle Puffer aktive Hoch-Drei-Zustands-Puffer.

Wenn der Decoder die ENA auf „HIGH“ setzt und der Datensatz „A“ aktiviert ist, kann der Mikrocontroller jetzt Daten über den Bus senden.

Die übrigen beiden Datensätze 'B' und 'C' befinden sich im Zustand 'HI-Z' oder sehr hochohmig, wodurch der Mikroprozessor und die logischen Schaltungen elektrisch vom Bus getrennt werden, der derzeit vom Mikrocontroller verwendet wird.

Wenn der Decoder ENB auf „HIGH“ setzt, kann der Datensatz „B“ Daten über den Bus senden, und die restlichen Datensätze „A“ und „C“ sind im Zustand „HI-Z“ vom Bus isoliert. Ebenso für den Fall, dass Datensatz 'C' aktiviert ist.

Der Datenbus wird von jedem der Datensätze 'A' oder 'B' oder 'C' zu einem bestimmten Zeitpunkt verwendet, um Konflikte zu vermeiden.

Wir können auch eine Duplex-Kommunikation (bidirektionale Kommunikation) herstellen, indem wir zwei Drei-Zustands-Puffer parallel und in entgegengesetzter Richtung verbinden. Die Freigabestifte können als Richtungssteuerung verwendet werden. Für solche Anwendungen kann der IC 74245 verwendet werden.

Hier ist die allgemein verfügbare Liste der digitalen Puffer und Tri-State-Puffer:

• 74LS07 Hex nicht invertierender Puffer

• 74LS17 Hex Buffer / Treiber

• 74LS244 Oktalpuffer / Leitungstreiber

• 74LS245 Oktaler bidirektionaler Puffer

• CD4050 Hex nicht invertierender Puffer

• CD4503 Hex Tri-State Buffer

• HEF40244 Drei-Zustands-Oktalpuffer

Damit ist unsere Diskussion über die Funktionsweise digitaler Puffer und ihre verschiedenen digitalen Konfigurationen abgeschlossen. Ich hoffe, Sie haben die Details besser verstanden. Wenn Sie weitere Fragen oder Anregungen haben, drücken Sie Ihre Fragen bitte im Kommentarbereich aus. Möglicherweise erhalten Sie eine schnelle Antwort.

Zurück: Funktionsweise von Logic Gates Weiter: Grundlegendes zu Pull-Up- und Pull-Down-Widerständen mit Diagrammen und Formeln